SPIDAT

Data RX

Data TX

SPI Module

GPIO MUX

Talk

SPICTL.1

Free pin

SPISISOx

Enhanced SPI Module Overview

959

SPRUH22I – April 2012 – Revised November 2019

Copyright © 2012–2019, Texas Instruments Incorporated

C28 Serial Peripheral Interface (SPI)

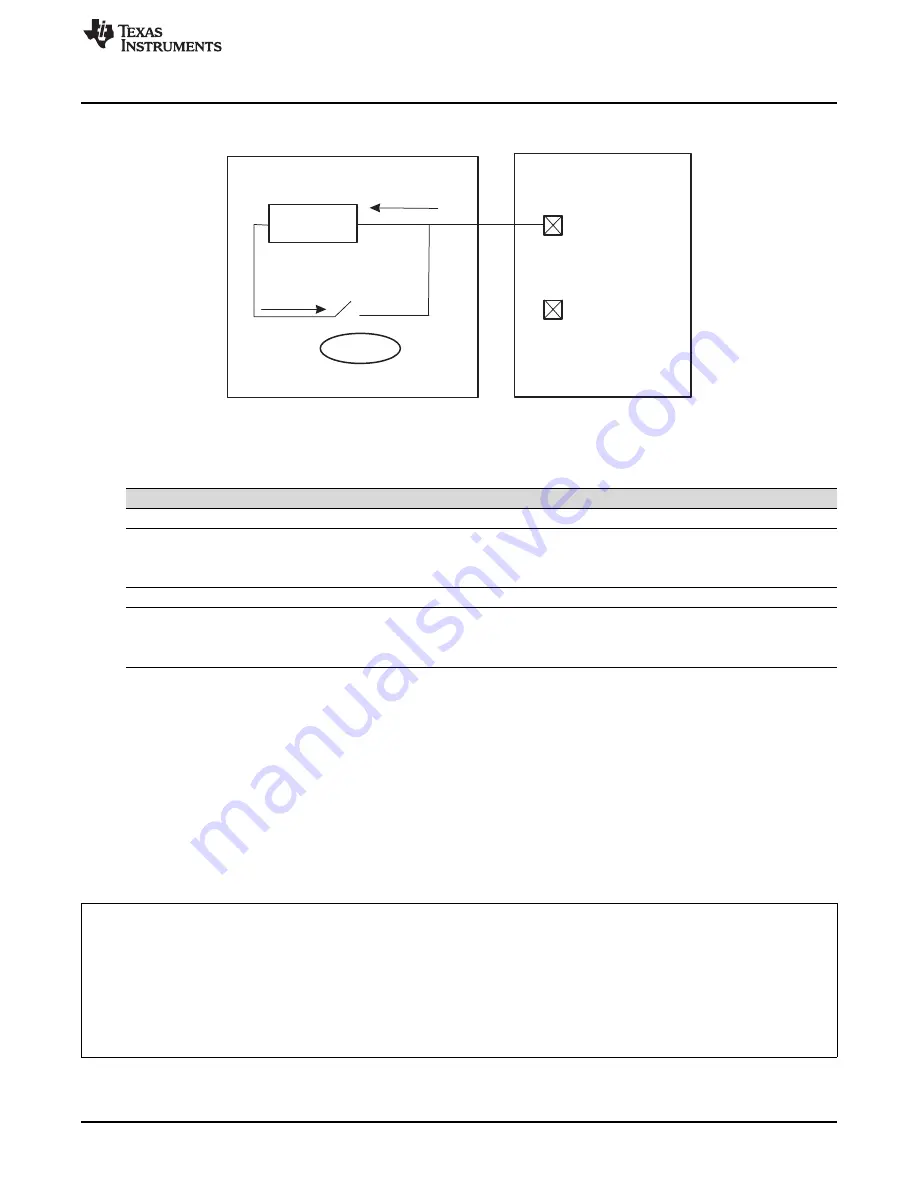

Figure 12-9. SPI 3-wire Slave Mode

indicates how data is received or transmitted in the various SPI modes while the TALK bit is

set or cleared.

Table 12-6. 3-Wire SPI Pin Configuration

Pin Mode

SPIPRI[TRIWIRE]

SPICTL[TALK]

SPISIMO

SPISOMI

Master Mode

4-wire

0

X

TX

RX

3-pin mode

1

0

RX

Disconnect from SPI

1

TX/RX

Slave Mode

4-wire

0

X

RX

TX

3-pin mode

1

0

Disconnect from SPI

RX

1

TX/RX

SPI 3-Wire Mode Code Examples

In addition to the normal SPI initialization, to configure the SPI module for 3-wire mode, the TRIWIRE bit

(SPIPRI.0) must be set to 1. After initialization, there are several considerations to take into account when

transmitting and receiving data in 3-wire master and slave mode. The following examples demonstrate

these considerations.

In 3-wire master mode, SPICLKx, SPISTEx, and SPISIMOx pins must be configured as SPI pins

(SPISOMIx pin can be configured as non-SPI pin). When the master transmits, it receives the data it

transmits (because SPISIMOx and SPISOMIx are connected internally in 3-wire mode). Therefore, the

junk data received must be cleared from the receive buffer every time data is transmitted.

Example 12-4. 3-Wire Master Mode Transmit

Uint16 data;

Uint16 dummy;

SpiaRegs.SPICTL.bit.TALK = 1;

// Enable Transmit path

SpiaRegs.SPITXBUF = data; // Master transmits data

while(SpiaRegs.SPISTS.bit.INT_FLAG !=1) {} // Waits until data rx’d

dummy = SpiaRegs.SPIRXBUF;

// Clears junk data from itself

// bc it rx’d same data tx’d