RAM Control Module

432

SPRUH22I – April 2012 – Revised November 2019

Copyright © 2012–2019, Texas Instruments Incorporated

Internal Memory

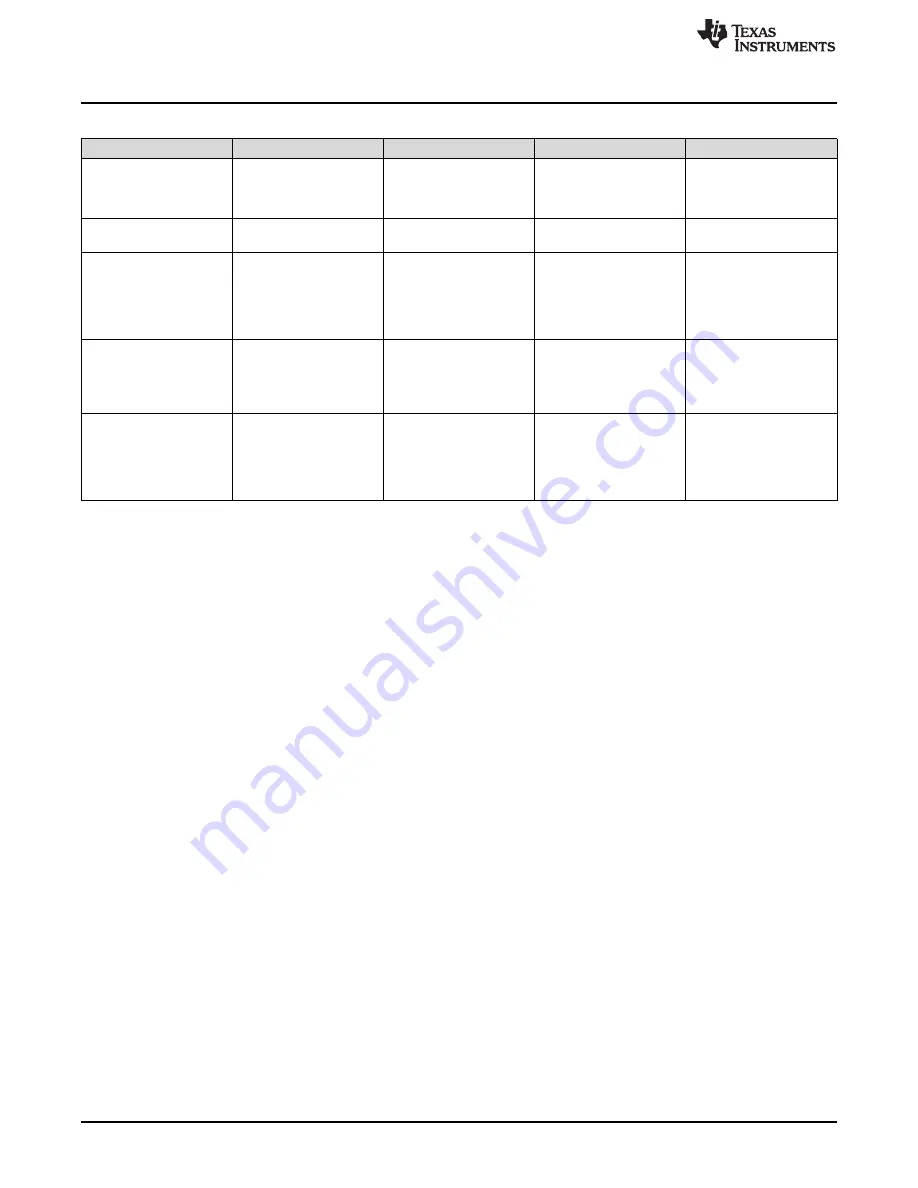

Table 5-2. Error Handling in Different Scenarios

Access Type

Error Found In

Error Type

Status Indication

Error Notification

M3/uDMA Byte Write (R-

M-W)

Data read from memory

Uncorrectable Error

(Parity Error OR Double

bit ECC Error)

M3/uDMA Write Address

Error Register – Indicates

address for which error

happened

NVIC Interrupt for uDMA

access / bus fault for M3

access

M3/uDMA Byte Write (R-

M-W)

Data read from memory

Correctable Error

No

None

Reads

Data read from memory

Uncorrectable Error

(Parity Error OR Double

bit ECC Error)

Yes - M3 / uDMA / C28

CPU / C28 DMA Read

Address Error Register

Data returned to M3 CPU

/ uDMA or C28 CPU / C28

DMA is incorrect

NMI for C28 CPU access

NMI for C28 DMA access

BUS FAULT for M3 CPU

access

Interrupt for uDMA access

Reads

Data read from memory

Single data error

Yes - M3 / uDMA / C28

CPU / C28 DMA Read

Address Error Register

Increment single error

counter

Interrupt on error counter

reaching the user

programmable threshold

for single errors

Reads

Address

Address error

Yes - M3 / uDMA / C28

CPU / C28 DMA Read

Address Error Register

Data returned to M3 CPU

/ uDMA or C28 CPU / C28

DMA is incorrect

NMI for C28 CPU access

NMI for C28 DMA access

BUS FAULT for M3 CPU

access

Interrupt for uDMA access

Notes:

In case of uncorrectable error duing fetch on C28x CPU, there is possibility of getting ITRAP

before NMI, since garbage instructions enters into C28x pipeline before NMI gets generated.

During debug accesses (RD/WR) correctable as well as uncorrectable errors are masked.

5.1.1.8

Application Test Hooks for Error Detection and Correction

Since error detection and correction logic is part of safety critical logic, safety applications may need to

ensure that the logic is working fine always (during run time also). To enable this, a RAMTEST mode is

provided. When “RAMTEST” mode is set (ECCPARTEST=1), the ECC/parity logic gets bypassed. For

example, while writing the data, only data bit’s will be written into memoy not the ECC/parity bits for data

and address. Using this feature an ECC/parity error could be injected into data. Also, the ECC/parity bits

for each address location are memory mapped in separate memory locations, accessible directly by the

CPU. The memory mapped ECC or parity bits can also be changed by the software. During read back, the

ECC / parity logic will detect an error thereby confirming to the application code that ECC/parity logic

works fine. If not then application should consider this as an error condition and handle it accordingly.

Notes:

The memory map for ECC/parity bits is accessible only when the RAMTEST mode is selected

(ECCPARTEST=1) or else reads to these address locations return ‘0.’

In RAMTEST mode, all access to memories (data as well as ECC/partiy) should be done as 32-bit access

only.

The following table shows the bit mapping for the ECC/parity bits when they are read in RAMTEST mode

using their respective addresses.