Section 21 Ethernet Controller Direct Memory Access Controller (E-DMAC)

Rev. 1.00 Mar. 12, 2008 Page 830 of 1178

REJ09B0403-0100

21.3.4

Multi-Buffer Frame Transmit/Receive Processing

Multi-Buffer Frame Transmit Processing

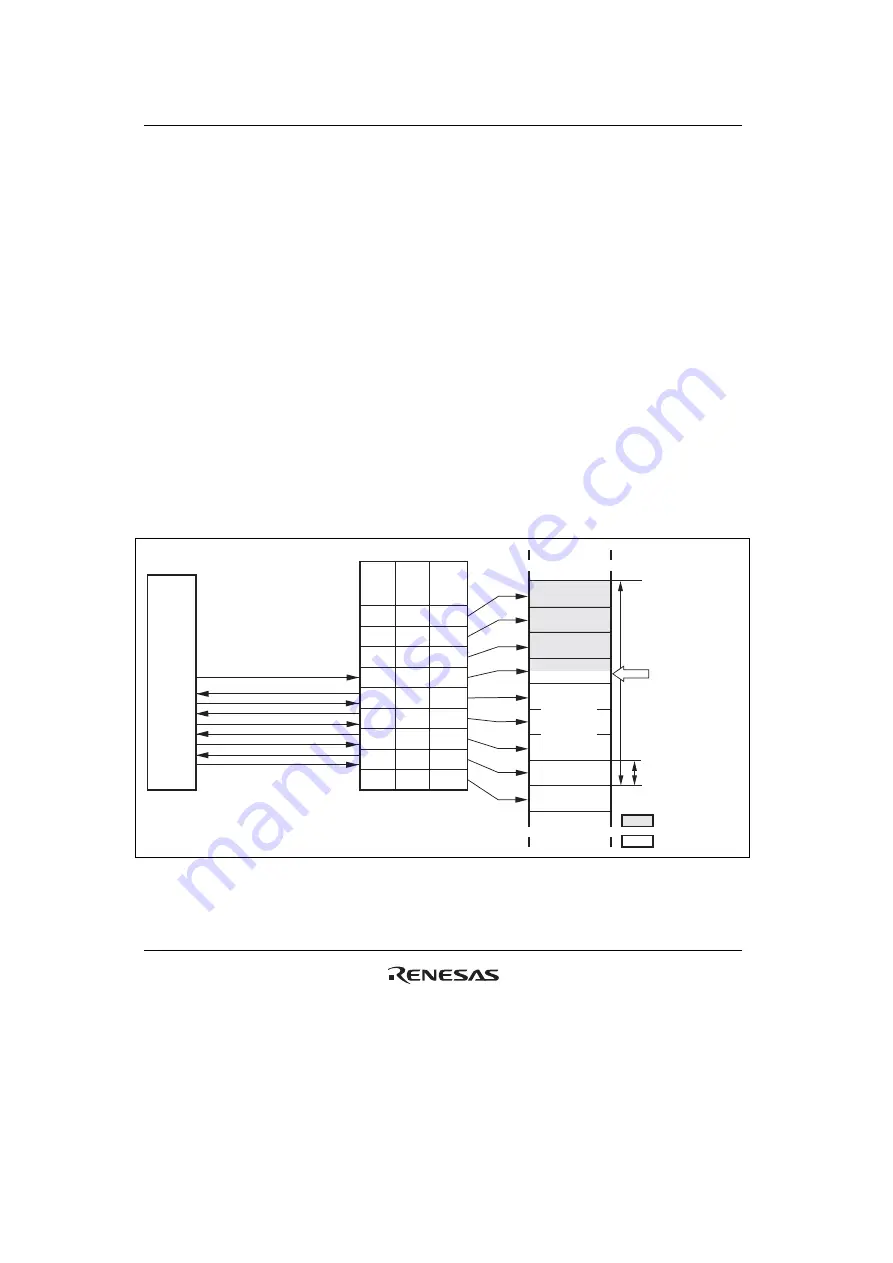

If an error occurs during multi-buffer frame transmission, the processing shown in figure 21.6 is

carried out by the E-DMAC.

Where the transmit descriptor is shown as inactive (TACT bit = 0) in the figure, buffer data has

already been transmitted normally, and where the transmit descriptor is shown as active (TACT bit

= 1), buffer data has not been transmitted. If a frame transmit error occurs in the first descriptor

part where the transmit descriptor is active (TACT bit = 1), transmission is halted, and the TACT

bit cleared to 0, immediately. The next descriptor is then read, and the position within the transmit

frame is determined on the basis of bits TFP1 and TFP0 (continuing [B'00] or end [B'01]). In the

case of a continuing descriptor, the TACT bit is cleared to 0, only, and the next descriptor is read

immediately. If the descriptor is the final descriptor, not only is the TACT bit cleared to 0, but

write-back is also performed to the TFE and TFS bits at the same time. Data in the buffer is not

transmitted between the occurrence of an error and write-back to the final descriptor. If error

interrupts are enabled in the EtherC/E-DMAC status interrupt permission register (EESIPR), an

interrupt is generated immediately after the final descriptor write-back.

0

0

0

1

1

1

1

1

1

0

0

0

0

0

0

0

0

1

1

0

0

0

0

0

0

0

1

0

0

0

0

0

0

0

1

0

E-DMAC

Inactivates TACT (change 1 to 0)

Descriptor read

Inactivates TACT

Descriptor read

Inactivates TACT

Descriptor read

Inactivates TACT

Descriptor read

Inactivates TACT and writes TFE, TFS

Descriptors

Untransmitted

data is not

transmitted

after error

occurrence

Descriptor is

only processed.

One frame

Buffer

Transmitted data

Untransmitted data

Transmit error

occurrence

T

A

C

T

T

D

L

E

T

F

P

1

T

F

P

0

Figure 21.6 E-DMAC Operation after Transmit Error

Summary of Contents for H8S Family

Page 2: ...Rev 1 00 Mar 12 2008 Page ii of xIviii...

Page 8: ...Rev 1 00 Mar 12 2008 Page viii of xIviii...

Page 28: ...Rev 1 00 Mar 12 2008 Page xxviii of xIviii...

Page 48: ...Rev 1 00 Mar 12 2008 Page xlviii of xIviii...

Page 70: ...Section 1 Overview Rev 1 00 Mar 12 2008 Page 22 of 1178 REJ09B0403 0100...

Page 108: ...Section 2 CPU Rev 1 00 Mar 12 2008 Page 60 of 1178 REJ09B0403 0100...

Page 116: ...Section 3 MCU Operating Modes Rev 1 00 Mar 12 2008 Page 68 of 1178 REJ09B0403 0100...

Page 152: ...Section 5 Interrupt Controller Rev 1 00 Mar 12 2008 Page 104 of 1178 REJ09B0403 0100...

Page 206: ...Section 6 Bus Controller BSC Rev 1 00 Mar 12 2008 Page 158 of 1178 REJ09B0403 0100...

Page 420: ...Section 9 14 Bit PWM Timer PWMX Rev 1 00 Mar 12 2008 Page 372 of 1178 REJ09B0403 0100...

Page 476: ...Section 12 Watchdog Timer WDT Rev 1 00 Mar 12 2008 Page 428 of 1178 REJ09B0403 0100...

Page 552: ...Section 14 CRC Operation Circuit CRC Rev 1 00 Mar 12 2008 Page 504 of 1178 REJ09B0403 0100...

Page 712: ...Section 18 I2 C Bus Interface IIC Rev 1 00 Mar 12 2008 Page 664 of 1178 REJ09B0403 0100...

Page 804: ...Section 19 LPC Interface LPC Rev 1 00 Mar 12 2008 Page 756 of 1178 REJ09B0403 0100...

Page 838: ...Section 20 Ethernet Controller EtherC Rev 1 00 Mar 12 2008 Page 790 of 1178 REJ09B0403 0100...

Page 964: ...Section 24 RAM Rev 1 00 Mar 12 2008 Page 916 of 1178 REJ09B0403 0100...

Page 1066: ...Section 25 Flash Memory Rev 1 00 Mar 12 2008 Page 1018 of 1178 REJ09B0403 0100...

Page 1098: ...Section 26 Boundary Scan JTAG Rev 1 00 Mar 12 2008 Page 1050 of 1178 REJ09B0403 0100...

Page 1226: ...Rev 1 00 Mar 12 2008 Page 1178 of 1178 REJ09B0403 0100...

Page 1229: ......

Page 1230: ...H8S 2472 Group H8S 2462 Group Hardware Manual...