Data

Data

S

1

Data

ACK

ACK

ACK

P

1

n

n

n

1

1

1

S

1

1 1 1 1 0 x x

7

x x x x x x x x

ACK

1

1

8

ACK

1

Data

n

ACK

1

P

1

x x = 2 MSBs

R/W

8 LSBs of slave address

S

7 bits of slave address

R/W

ACK

Data

ACK

Data

ACK

P

7

n

n

1

1

1

1

1

1

x x x x x x x

SDA

SCL

MSB

Acknowledgement

bit from slave

(No-)Acknowledgement

bit from receiver

1

2

7

8

9

1

2

8

9

Slave address

ACK

START

condition (S)

STOP

condition (P)

R/W

ACK

Data

I2C Module Operational Details

1051

SPRUHE8E – October 2012 – Revised November 2019

Copyright © 2012–2019, Texas Instruments Incorporated

C28 Inter-Integrated Circuit Module

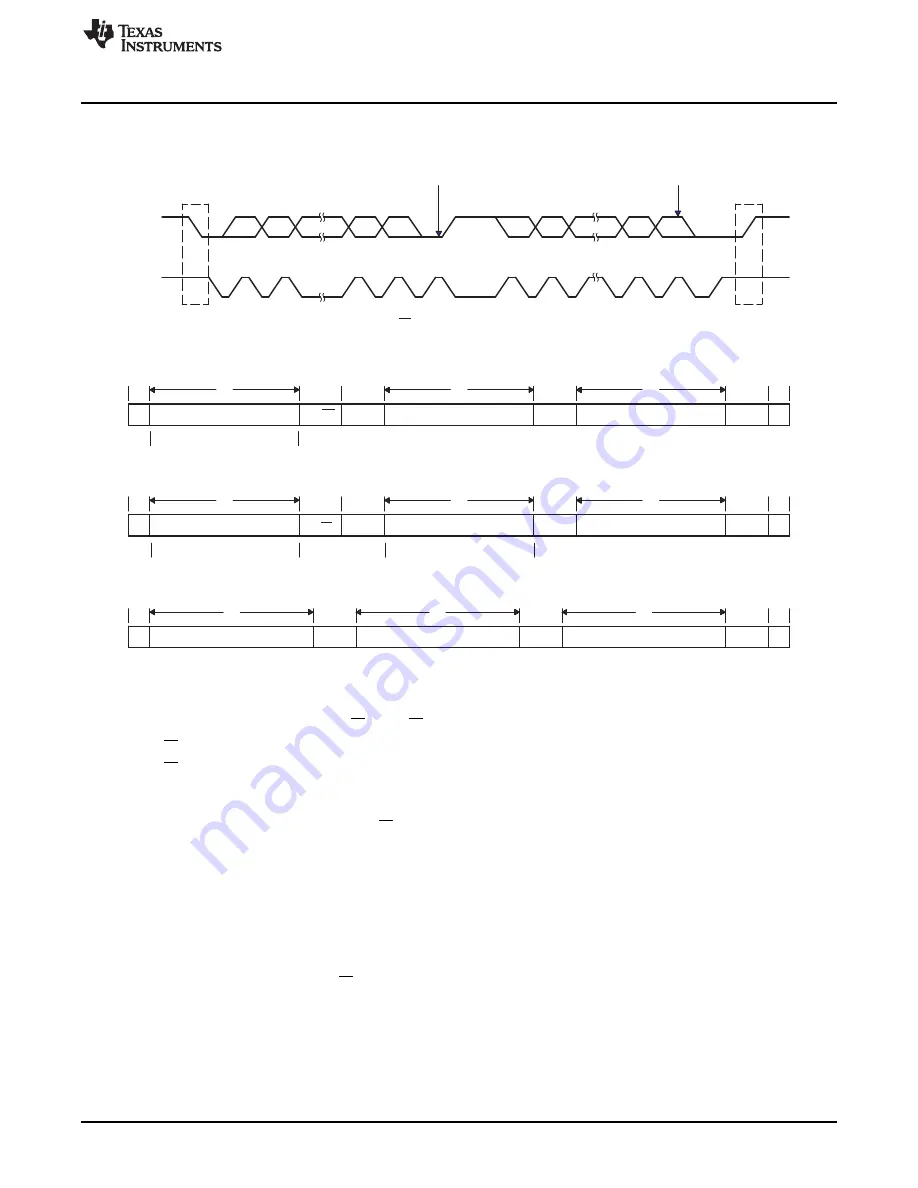

Figure 14-6. I2C Module Data Transfer (7-Bit Addressing with 8-bit Data Configuration Shown)

Figure 14-7. I2C Module 7-Bit Addressing Format (FDF = 0, XA = 0 in I2CMDR)

Figure 14-8. I2C Module 10-Bit Addressing Format (FDF = 0, XA = 1 in I2CMDR)

Figure 14-9. I2C Module Free Data Format (FDF = 1 in I2CMDR)

14.2.5.1 7-Bit Addressing Format

In the 7-bit addressing format (see

), the first byte after a START condition (S) consists of a 7-

bit slave address followed by a R/W bit. R/W determines the direction of the data:

•

R/W = 0: The master writes (transmits) data to the addressed slave.

•

R/W = 1: The master reads (receives) data from the slave.

An extra clock cycle dedicated for acknowledgment (ACK) is inserted after each byte. If the ACK bit is

inserted by the slave after the first byte from the master, it is followed by n bits of data from the transmitter

(master or slave, depending on the R/W bit). n is a number from 1 to 8 determined by the bit count (BC)

field of I2CMDR. After the data bits have been transferred, the receiver inserts an ACK bit.

To select the 7-bit addressing format, write 0 to the expanded address enable (XA) bit of I2CMDR, and

make sure the free data format mode is off (FDF = 0 in I2CMDR).

14.2.5.2 10-Bit Addressing Format

The 10-bit addressing format (see

) is similar to the 7-bit addressing format, but the master

sends the slave address in two separate byte transfers. The first byte consists of 11110b, the two MSBs of

the 10-bit slave address, and R/W = 0 (write). The second byte is the remaining 8 bits of the 10-bit slave

address. The slave must send acknowledgment after each of the two byte transfers. Once the master has

written the second byte to the slave, the master can either write data or use a repeated START condition

to change the data direction. For more details about using 10-bit addressing, see the Philips

Semiconductors I2C-bus specification.

To select the 10-bit addressing format, write 1 to the XA bit of I2CMDR and make sure the free data

format mode is off (FDF = 0 in I2CMDR).