CAN Control Registers

1585

SPRUHE8E – October 2012 – Revised November 2019

Copyright © 2012–2019, Texas Instruments Incorporated

M3 Controller Area Network (CAN)

NOTE:

For debug support, the auto clear functionality of Error and Status Register (clear of status

flags by read) is disabled when in Debug mode.

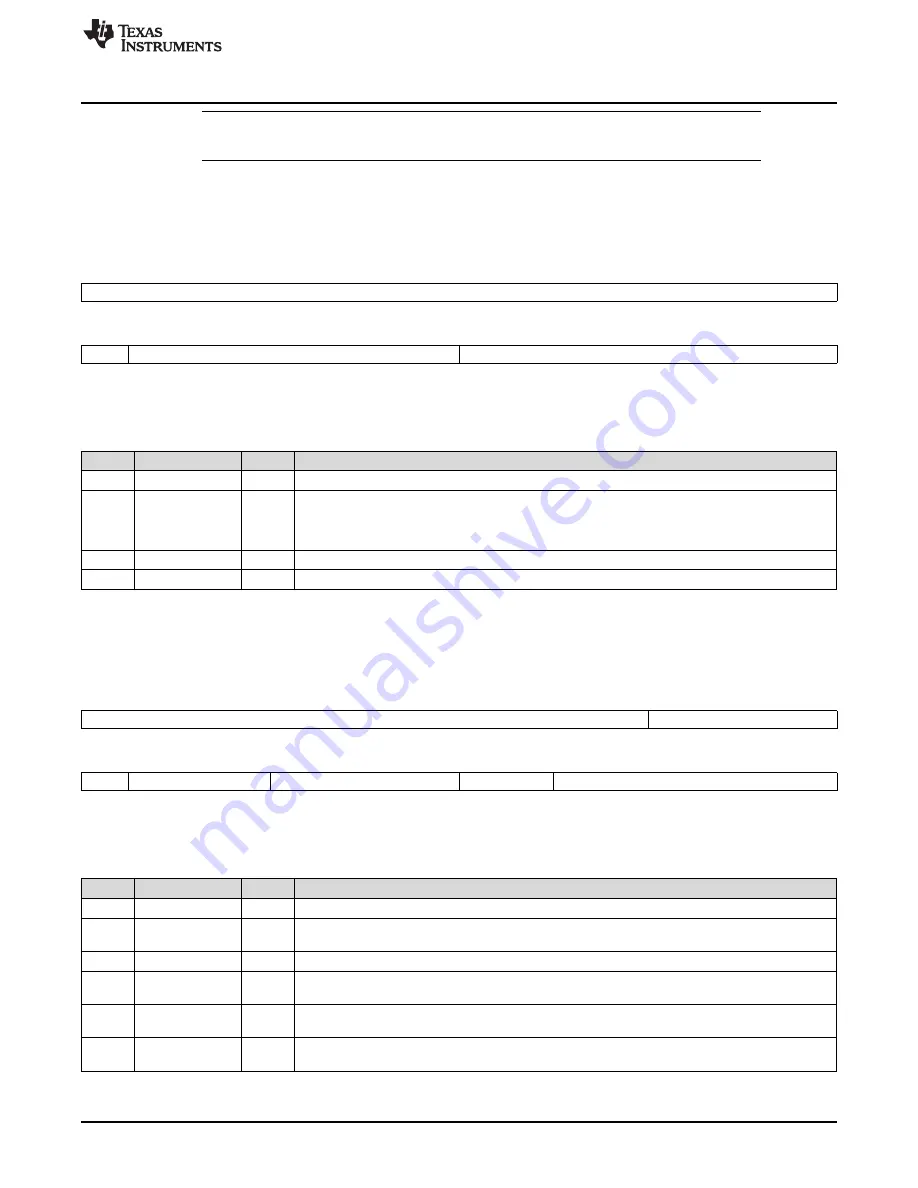

23.15.3 Error Counter Register (CAN ERRC)

The Error Counter register (CAN ERRC) is shown and described in the figure and table below.

Figure 23-21. Error Counter Register (CAN ERRC) [offset = 0x08]

31

16

Reserved

R-0

15

14

8

7

0

RP

REC[6:0]

TEC[7:0]

R-0

R-0

R-0

LEGEND: R = Read; -

n

= value after reset

Table 23-7. Error Counter Register Field Descriptions

Bit

Field

Value

Description

31-16

Reserved

Reserved

15

RP

Receive Error Passive

0

The Receive Error Counter is below the error passive level.

1

The Receive Error Counter has reached the error passive level as defined in the CAN Specification.

14-8

REC[6:0]

Receive Error Counter. Actual state of the Receive Error Counter (values from 0 to 255).

7-0

TEC[7:0]

Transmit Error Counter. Actual state of the Transmit Error Counter (values from 0 to 255).

23.15.4 Bit Timing Register (CAN BTR)

The Bit Timing register (CAN BTR) is shown and described in the figure and table below.

Figure 23-22. Bit Timing Register (CAN BTR) [offset = 0x0C]

31

20

19

16

Reserved

BRPE

R-0

R/WP-0

15

14

12

11

8

7

6

5

0

Rsvd

TSeg2

TSeg1

SJW

BRP

R-0

R/WP-0x2

R/WP-0x3

R/WP-0

R/WP-0x1

LEGEND: R = Read; WP = Write Protected by CCE bit; -

n

= value after reset

Table 23-8. Bit Timing Register Field Descriptions

Bit

Field

Value

Description

31-20

Reserved

Reserved

19-16

BRPE

0x00-

0x0F

Baud Rate Prescaler Extension. Valid programmed values are 0 to 15. By programming BRPE the

Baud Rate Prescaler can be extended to values up to 1024.

15

Reserved

Reserved

14-12

TSeg2

0x0-0x7 Time segment after the sample point Valid programmed values are 0 to 7. The actual TSeg2 value

which is interpreted for the Bit Timing will be the programmed TSeg2 value + 1.

11-8

TSeg1

0x01-

0x0F

Time segment before the sample point Valid programmed values are 1 to 15. The actual TSeg1

value interpreted for the Bit Timing will be the programmed TSeg1 value + 1.

7-6

SJW

0x0-0x3 Synchronization Jump Width Valid programmed values are 0 to 3. The actual SJW value

interpreted for the Synchronization will be the programmed SJW value + 1.