Safety Features

122

SPRUHE8E – October 2012 – Revised November 2019

Copyright © 2012–2019, Texas Instruments Incorporated

System Control and Interrupts

11. On the control subsystem, the CLOCKFAIL signal is also fed to TZ5n trip signal of all the PWM

modules. This allows the PWM outputs to trip in case of clock failure.

12. When a missing clock condition is detected, the counters are disabled. They need to be re-enabled by

software after all error handling and when a proper clock source is available again

NOTE:

[1]

On a clock fail condition, nothing is done in hardware to enter standby mode on the C28

side. When a CLOCKFAIL NMI is generated, the C28 application software should configure

the LPMCR registers to enter standby mode.

[2]

Changing the clock limit values (REFCLKLO and HI limit) should be done after disabling

the missing clock NMI, using the MCLKNMIEN bit in the MCLKEN register. After the

registers are programmed for appropriate input clock frequencies, the MCLKNMIEN bit

should be set again after at least a 900ns delay.

[3]

At power up, the circuit only checks whether the clock is ticking or not because the limits

encompass the entire range of clock input frequencies allowed in the device.

Example of clock limit register configuration:

Internal Oscillator is at 10 MHz; 3-bit 10 MHz clock

counter overflows every 800ns.

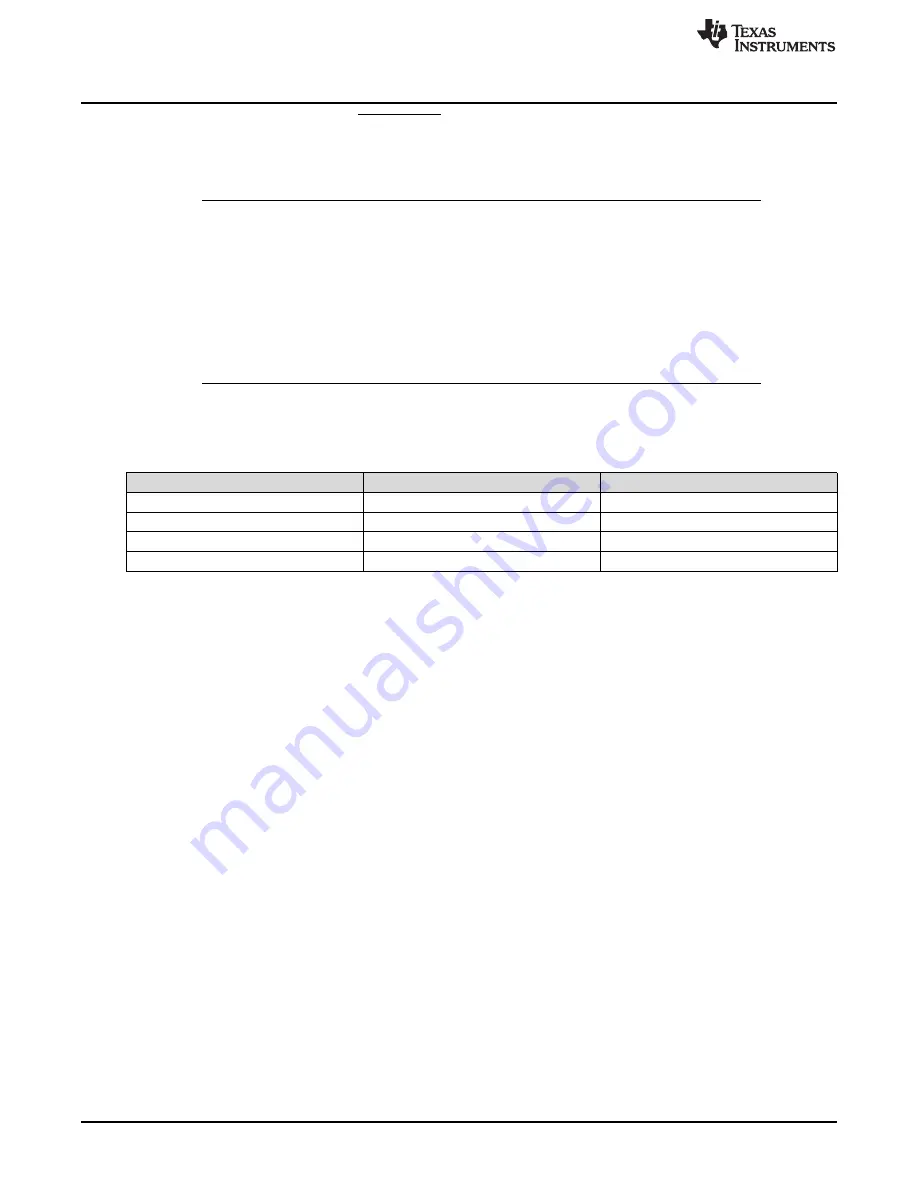

Table 1-15. Reference Clock Limits for Detecting a Missing Clock

Ref Clock Frequency

REFCLKLOLIMIT

REFCLKHILIMIT

4 MHz (250ns)

0x3

0x4

10 MHz (100ns)

0x7

0x9

20 MHz (50ns)

0xF

0x11

100 MHz (10ns)

0x4E

0x52