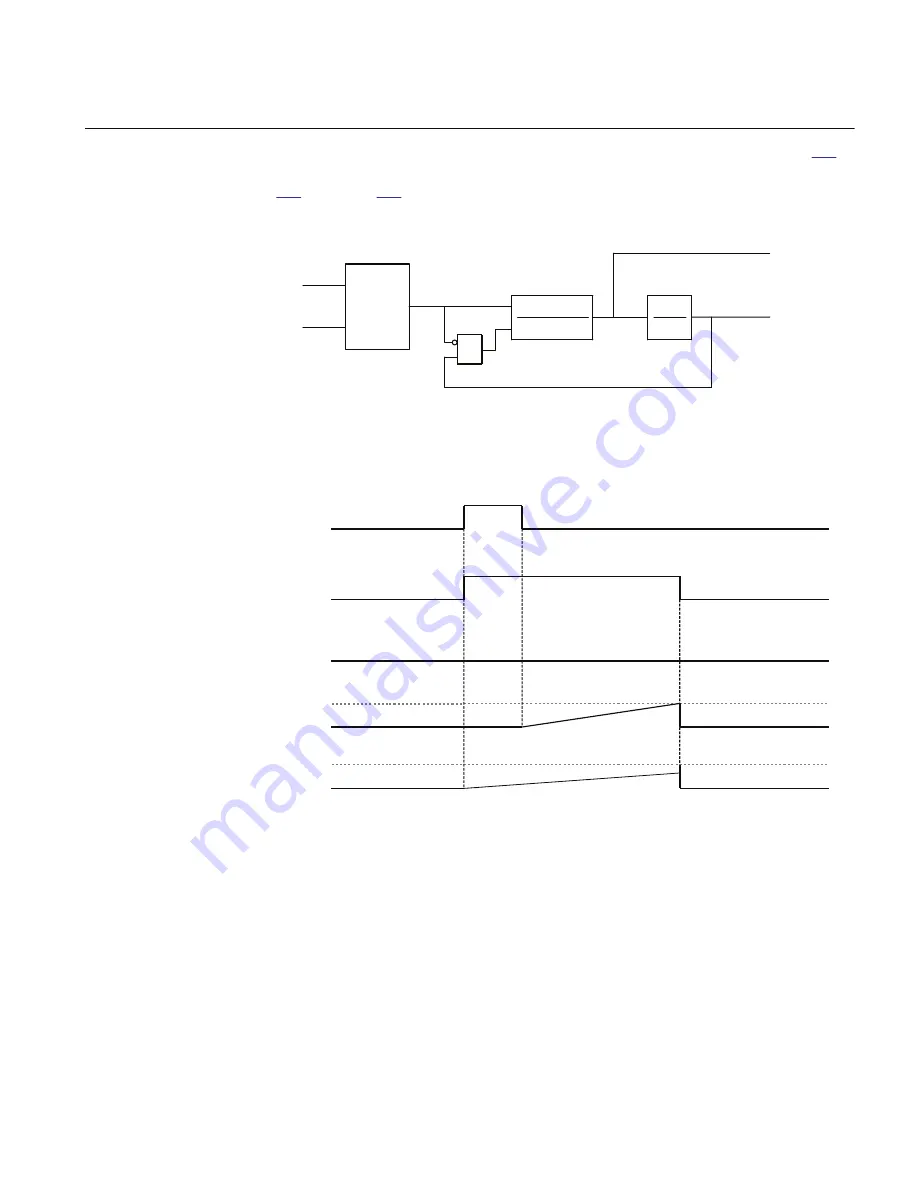

When definite time delay is selected the function will operate as shown in figure

.

Detailed information about individual stage reset/operation behavior is shown in figure

and figure

respectively. Note that by setting

tResetn

=

0.0s

, instantaneous reset

of the definite time delayed stage is ensured.

a<b

a

b

Pickup1

V

TRST1

PU_ST1

AND

0

t1

tReset1

0

R

ANSI09000785-3-en.vsd

ANSI09000785 V3 EN

Figure 251:

Detailed logic diagram for step 1, DT operation

Pickup1

PU_ST1

TRST1

tReset1

t1

ANSI10000039-3-en.vsd

ANSI10000039 V3 EN

Figure 252:

Example for Definite Time Delay stage1 reset

1MRK505222-UUS C

Section 8

Voltage protection

497

Technical reference manual

Summary of Contents for Relion 670 series

Page 1: ...Relion 670 series Line differential protection RED670 ANSI Technical reference manual...

Page 2: ......

Page 40: ...34...

Page 50: ...44...

Page 60: ...54...

Page 126: ...120...

Page 384: ...378...

Page 496: ...490...

Page 556: ...550...

Page 602: ...596...

Page 620: ...614...

Page 794: ...788...

Page 864: ...858...

Page 988: ...982...

Page 998: ...992...

Page 1084: ...1078...

Page 1164: ...1158...

Page 1168: ...1162...

Page 1220: ...1214...

Page 1230: ...1224...

Page 1231: ...1225...