CHAPTER 8 8-BIT TIMER/EVENT COUNTER 5

User’s Manual U16896EJ2V0UD

302

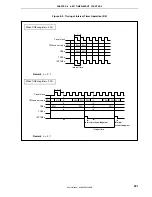

8.4.2 Operation as external event counter

The external event counter counts the number of clock pulses input to the TI5n pin from an external source by

using the TM5n register.

Each time the valid edge specified by the TCL5n register is input to the TI5n pin, the TM5n register is incremented.

Either the rising edge or the falling edge can be specified as the valid edge.

When the count value of the TM5n register matches the value of the CR5n register, the TM5n register is cleared to

00H and an interrupt request signal (INTTM5n) is generated.

Setting method

<1> Set each register.

•

TCL5n register: Selects the TI5n pin input edge.

Falling edge of TI5n pin

→

TCL5n register = 00H

Rising edge of TI5n pin

→

TCL5n register = 01H

•

CR5n register:

Compare value (N)

•

TMC5n register: Stops count operation, selects the mode in which clear & start occurs on a match

between the TM5n register and CR5n register, disables timer output F/F inversion

operation, and disables timer output.

(TMC5n register = 0000xx00B,

×

: don’t care)

•

For the alternate-function pin settings, refer to

Table 4-12 Settings When Port Pins Are Used for

Alternate Functions.

<2> When the TMC5n.TCE5n bit is set to 1, the counter counts the number of pulses input from the TI5n pin.

<3> When the values of the TM5n register and CR5n register match, the INTTM5n signal is generated (TM5n

register is cleared to 00H).

<4> Then, the INTTM5n signal is generated each time the values of the TM5n register and CR5n register

match.

INTTM5n signal is generated when the valid edge is input to the TI5n pin N + 1 times: N = 00H to FFH

Caution During external event counter operation, do not rewrite the value of the CR5n register.

Remark

n = 0, 1

Figure 8-3. Timing of External Event Counter Operation (with Rising Edge Specified)

00H

01H

02H

03H

04H

05H

N

−

1

N

N

00H

01H

02H

03H

TI5n

CR5n

INTTM5n

TCE5n

TM5n count value

Count start

Remark

n = 0, 1