CHAPTER 7 16-BIT TIMER/EVENT COUNTER 0

User’s Manual U16896EJ2V0UD

236

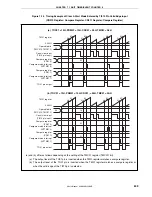

(4) Prescaler mode register 01 (PRM01)

The PRM01 register is the register that sets the TM01 register count clock and TI010 and TI011 pin input valid

edges. The PRM011 and PRM010 bits are set in combination with the SELCNT1.ISEL11 bit. Refer to

7.3 (6)

Count clock setting for 16-bit timer/event counter 01

for details.

Rewriting the PRM01 register is prohibited during operation (when the TMC01.TMC013 and TMC01.TMC012 bits

= other than 00).

This register can be read or written in 8-bit or 1-bit units.

Reset sets this register to 00H.

Cautions 1. Do not apply the following setting when setting the PRM011 and PRM010 bits to 11 (to

specify the valid edge of the TI010 pin as a count clock).

•

Clear & start mode entered by the TI010 pin valid edge

•

Setting the TI010 pin as a capture trigger

2. If the operation of the 16-bit timer/event counter 01 is enabled when the TI010 or TI011 pin is

at high level and when the valid edge of the TI010 or TI011 pin is specified to be the rising

edge or both edges, the high level of the TI010 or TI011 pin is detected as a rising edge.

Note this when the TI010 or TI011 pin is pulled up. However, the rising edge is not detected

when the timer operation has been once stopped and is then enabled again.

3. When the P35 pin is used as the valid edge of TI010 and the timer output function is used,

set the P32 pin as the timer output pin (TO01).

ES111

ES110

TI011 pin valid edge selection

0 0

Falling

edge

0 1

Rising

edge

1 0

Setting

prohibited

1

1

Both falling and rising edges

ES101

ES100

TI010 pin valid edge selection

0 0

Falling

edge

0 1

Rising

edge

1 0

Setting

prohibited

1

1

Both falling and rising edges

Remark

For setting of the PRM011 and PRM010 bits, refer to

7.3 (6) Count clock setting for 16-bit

timer/event counter 01

.

After reset: 00H R/W

Address:

FFFFF617H

7 6 5 4 3 2 1 0

PRM01 ES111 ES110 ES101 ES100

0

0 PRM011

PRM010