CHAPTER 17 INTERRUPT/EXCEPTION PROCESSING FUNCTION

User’s Manual U16896EJ2V0UD

533

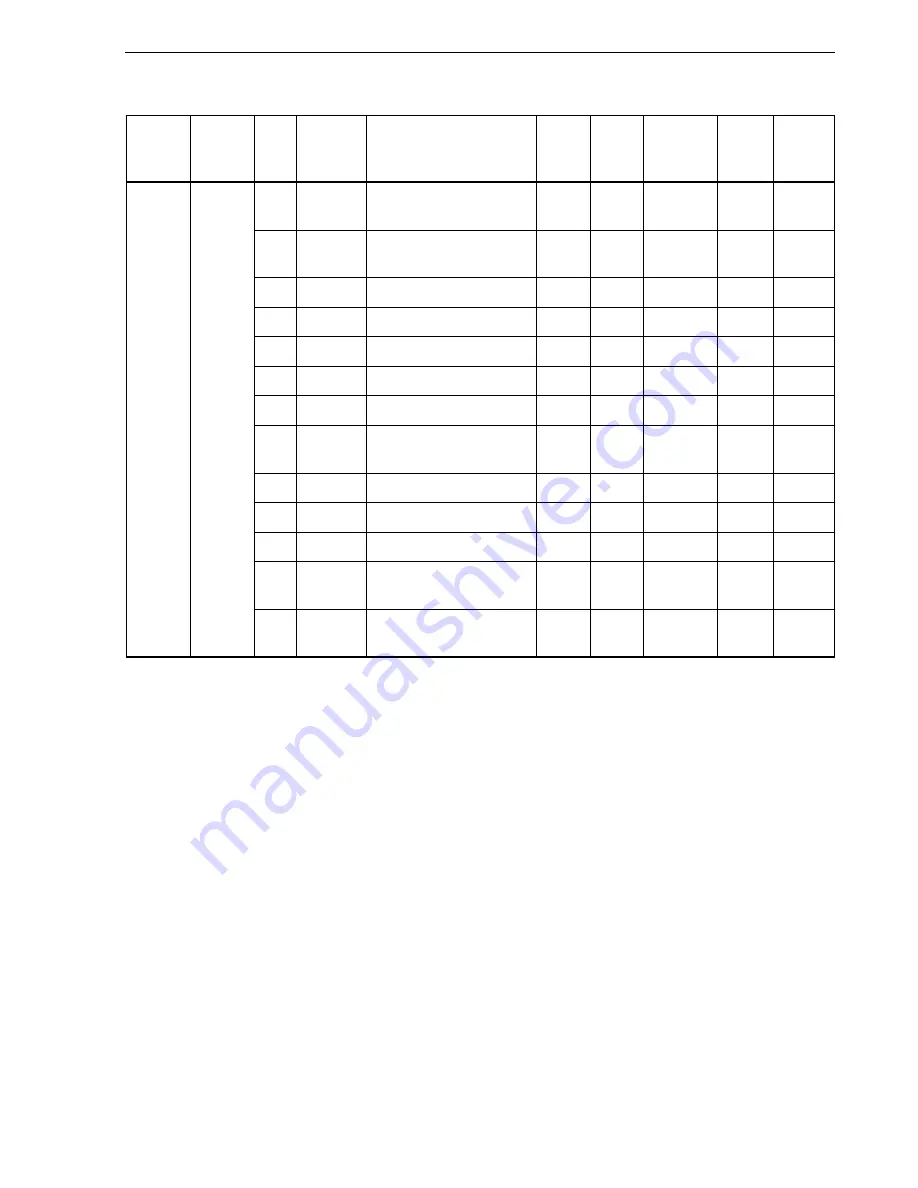

Table 17-1. Interrupt Source List (2/2)

Type

Classification Default

Priority

Name Trigger

Interrupt

Source

Exception

Code

Handler

Address

Restored

PC

Interrupt

Control

Register

22 INTTMH0 TMH0

and

CMP00/CMP01

match

TMH0 01E0H 000001E0H

nextPC TMHIC0

23 INTTMH1 TMH1

and

CMP10/CMP11

match

TMH1 01F0H 000001F0H

nextPC TMHIC1

25 INTIIC0

Note

I

2

C0 transfer completion

I

2

C0 0210H

00000210H

nextPC

IICIC0

26 INTAD

A/D

conversion

completion A/D

0220H 00000220H nextPC ADIC

27

INTKR

Key return interrupt

KR 0230H

00000230H

nextPC

KRIC

28

INTWTI

Watch timer interval

WT

0240H

00000240H nextPC

WTIIC

29

INTWT

Watch timer reference time

WT 0250H

00000250H

nextPC

WTIC

30

INTBRG

8-bit counter of prescaler 3

and PRSCM match

Prescaler 3

0260H 00000260H nextPC BRGIC

45 INTLVI

Low-voltage

detection

LVI

0380H 00000380H nextPC LVIIC

46

INTP7

INTP7 pin valid edge input

Pin

0390H

00000390H nextPC

PIC7

47 INTTP0OV

TMP0

overflow

TMP 03A0H 000003A0H

nextPC TP0OVIC

48

INTTP0CC0 TMP0 capture 0/

compare 0 match

TMP 03B0H

000003B0H

nextPC

TP0CCIC0

Maskable Interrupt

49

INTTP0CC1 TMP0 capture 1/

compare 1 match

TMP 03C0H

000003C0H

nextPC

TP0CCIC1

Note

Only in the

μ

PD703302Y, 70F3302Y

Remarks 1.

Default priority: The priority order when two or more maskable interrupt requests with the same

priority level are generated at the same time. The highest priority is 0.

The priority of non-maskable interrupt request is as follows.

INTWDT2 > INTWDT1 > NMI

Restored PC: The value of the program counter (PC) saved to EIPC, FEPC, or DBPC when

interrupt/exception processing is started. The restored PC when a non-maskable or

maskable interrupt is acknowledged while either of the following instructions is being

executed does not become nextPC (when an interrupt is acknowledged during the

execution of an instruction, the execution of that instruction is stopped and is

resumed following completion of interrupt servicing).

•

Load instructions (SLD.B, SLD.BU, SLD.H, SLD.HU, SLD.W)

•

Divide instructions (DIV, DIVH, DIVU, DIVHU)

•

PREPARE, DISPOSE instructions (only when an interrupt occurs before stack

pointer update)

nextPC:

The PC value at which processing is started following interrupt/exception processing.

2.

The execution address of the illegal opcode when an illegal opcode exception occurs is calculated

with (Restored PC – 4).