CHAPTER 17 INTERRUPT/EXCEPTION PROCESSING FUNCTION

User’s Manual U16896EJ2V0UD

537

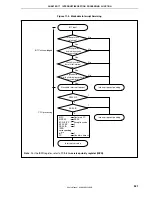

17.2.1 Operation

Upon generation of a non-maskable interrupt request signal, the CPU performs the following processing and

transfers control to a handler routine.

<1> Saves the restored PC to FEPC.

<2> Saves the current PSW to FEPSW.

<3> Writes the exception code (0010H, 0020H, 0030H) to the higher halfword (FECC) of ECR.

<4> Sets the PSW.NP and PSW.ID bits to 1 and clears the PSW.EP bit to 0.

<5> Loads the handler address (00000010H, 00000020H, 00000030H) of the non-maskable interrupt to the PC

and transfers control.

Figure 17-2 shows the servicing flow for non-maskable interrupts.

Figure 17-2. Non-Maskable Interrupt Servicing

NMI input

Non-maskable interrupt request

Interrupt servicing

Interrupt request held pending

FEPC

FEPSW

ECR. FECC

PSW. NP

PSW. EP

PSW. ID

PC

Restored PC

PSW

Exception code

1

0

1

Handler address

INTC acknowledged

CPU processing

PSW. NP

1

0