CHAPTER 17 INTERRUPT/EXCEPTION PROCESSING FUNCTION

User’s Manual U16896EJ2V0UD

547

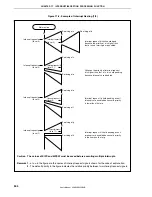

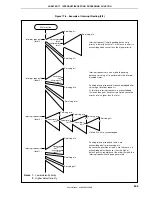

17.3.4 Interrupt control register (xxlCn)

An interrupt control register is assigned to each maskable interrupt and sets the control conditions for each

maskable interrupt request. The interrupt control registers can be read or written in 8-bit or 1-bit units.

Reset sets this register to 47H.

Caution Be sure to read the xxICn.xxIFn bit while interrupts are disabled (DI). If the xxIFn bit is read while

interrupts are enabled (EI), an incorrect value may be read if there is a conflict between

acknowledgment of the interrupt and reading of the bit.

xxIFn

Interrupt request not generated

Interrupt request generated

xxIFn

0

1

Interrupt request flag

Note

xxICn

xxMKn

0

0

0

xxPRn2

xxPRn1

xxPRn0

Enables interrupt servicing

Disables interrupt servicing (pending)

xxMKn

0

1

Interrupt mask flag

Specifies level 0 (highest)

Specifies level 1

Specifies level 2

Specifies level 3

Specifies level 4

Specifies level 5

Specifies level 6

Specifies level 7 (lowest)

xxPRn2

0

0

0

0

1

1

1

1

Interrupt priority specification bit

xxPRn1

0

0

1

1

0

0

1

1

xxPRn0

0

1

0

1

0

1

0

1

After reset: 47H R/W Address: FFFFF110H to FFFFF168H

< >

< >

Note

Automatically reset by hardware when interrupt request is acknowledged.

Remark

xx: Identifying name of each peripheral unit (refer to

Table 17-2 Interrupt Control Registers

(xxICn)

)

n: Peripheral unit number (refer to

Table 17-2 Interrupt Control Registers (xxICn)

)

Following tables list the addresses and bits of the interrupt control registers.