CHAPTER 24 ROM CORRECTION FUNCTION

User’s Manual U16896EJ2V0UD

622

24.2.2 Correction control register (CORCN)

This register disables or enables the correction operation at the address specified by the CORADn register.

Each channel can be enabled or disabled by this register.

This register can be read or written in 8-bit or 1-bit units.

Reset sets this register 00H.

0

Disabled

Enabled

CORENn

0

1

Correction operation enable/disable

CORCN

0

0

0

COREN3 COREN2 COREN1 COREN0

After reset: 00H R/W Address: FFFFF880H

< >

< >

< >

< >

Remark

n = 0 to 3

Table 24-2. Correspondence Between CORCN Register Bits and CORADn Registers

CORCN Register Bit

Corresponding CORADn Register

COREN3 CORAD3

COREN2 CORAD2

COREN1 CORAD1

COREN0 CORAD0

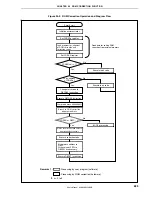

24.3 ROM Correction Operation and Program Flow

<1> If the address to be corrected and the fetch address of the internal ROM match, the fetch code is replaced by

the DBTRAP instruction.

<2> When the DBTRAP instruction is executed, execution branches to address 00000060H.

<3> Software processing after branching causes the result of ROM correction to be judged (the fetch address and

ROM correction operation are confirmed) and execution to branch to the correction software.

<4> After the correction software has been executed, the return address is set, and return processing is started

by the DBRET instruction.

Cautions 1. The software that performs <3> and <4> must be executed in the external memory or internal

RAM.

2. When setting an address to be corrected to the CORADn register, clear the higher bits to 0 in

accordance with the capacity of the internal ROM.

3. The ROM correction function cannot be used to correct the data of the internal ROM. It can

only be used to correct instruction codes. If ROM correction is used to correct data, that data

is replaced with the DBTRAP instruction code.