CHAPTER 6 16-BIT TIMER/EVENT COUNTER P (TMP)

User’s Manual U16896EJ2V0UD

177

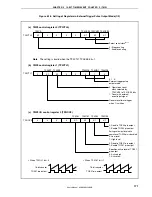

(b) 0%/100% output of PWM waveform

To output a 0% waveform, clear the TP0CCR1 register to 0000H. If the set value of the TP0CCR0 register

is FFFFH, the INTTP0CC1 signal is generated periodically.

Count clock

16-bit counter

TP0CE bit

TP0CCR0 register

TP0CCR1 register

INTTP0CC0 signal

INTTP0CC1 signal

TOP01 pin output

D

0

0000H

D

0

0000H

D

0

0000H

D

0

−

1

D

0

0000

FFFF

0000

D

0

−

1

D

0

0000

0001

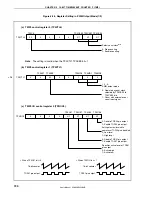

To output a 100% waveform, set a value of (set value of TP0CCR0 re 1) to the TP0CCR1 register.

If the set value of the TP0CCR0 register is FFFFH, 100% output cannot be produced.

Count clock

16-bit counter

TP0CE bit

TP0CCR0 register

TP0CCR1 register

INTTP0CC0 signal

INTTP0CC1 signal

TOP01 pin output

D

0

D

0

+ 1

D

0

D

0

+ 1

D

0

D

0

+ 1

D

0

−

1

D

0

0000

FFFF

0000

D

0

−

1

D

0

0000

0001

<R>