CHAPTER 9 8-BIT TIMER H

User’s Manual U16896EJ2V0UD

324

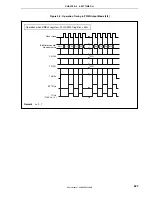

<3> After the count operation is enabled, the first compare register to be compared is the CMPn0 register.

When the count value of 8-bit timer counter Hn and the set value of the CMPn0 register match, 8-bit timer

counter Hn is cleared, an interrupt request signal (INTTMHn) is generated, and the TOHn output level is

inverted. At the same time, the register that is compared with 8-bit timer counter Hn changes from the

CMPn0 register to the CMPn1 register.

<4> When the count value of 8-bit timer counter Hn and the set value of the CMPn1 register match, the TOHn

output level is inverted, and at the same time the register that is compared with 8-bit timer counter Hn

changes from the CMPn1 register to the CMPn0 register. At this time, 8-bit timer counter Hn is not cleared

and the INTTMHn signal is not generated.

<5> A pulse of any duty can be obtained through the repetition of steps <3> and <4> above.

<6> To stop the count operation, clear the TMHEn bit to 0.

Designating the set value of the CMPn0 register as (N), the set value of the CMPn1 register as (M), and the count

clock frequency as f

CNT

, the PWM pulse output cycle and duty are as follows.

PWM pulse output cycle = (N + 1)/f

CNT

Duty = Inactive width: Active width = (M + 1) : (N + 1)

Cautions 1. The set value of the CMPn1 register can be changed while the timer counter is operating.

However, this takes a duration of at least three operating clocks (signal selected by the

TMHMDn.CKSHn2 to TMHMDn.CKSHn0 bits) from when the value of the CMPn1 register is

changed until the value is transferred to the register.

2. Be sure to set the CMPn1 register when starting the timer count operation (TMHEn bit = 1)

after the timer count operation was stopped (TMHEn bit = 0) (be sure to set again even if

setting the same value to the CMPn1 register).

3. Make sure that the CMPn1 register set value (M) and CMPn0 register set value (N) are within

the following range.

00H

≤

CMPn1 (M) < CMPn0 (N)

≤

FFH

<R>

<R>