CHAPTER 7 16-BIT TIMER/EVENT COUNTER 0

User’s Manual U16896EJ2V0UD

273

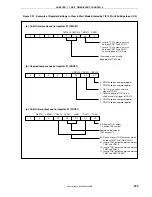

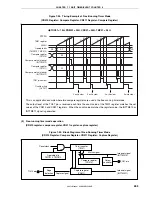

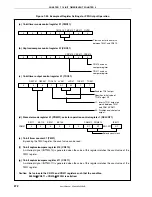

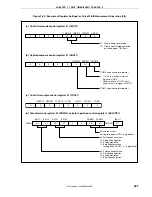

Figure 7-33. Example of Software Processing for PPG Output Operation

TM01 register

0000H

Operable bits

(TMC013, TMC012)

Compare register

(CR010)

Compare match interrupt

(INTTM010)

Compare register

(CR011)

Compare match interrupt

(INTTM011)

Timer output control bits

(TOE01, TOC014, TOC011)

TO01 pin output

M

11

M

M

M

N

N

N

00

<1>

N + 1

<2>

00

N

TMC013, TMC012 bits = 11

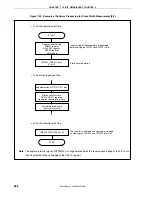

Register initial setting

PRM01 register,

SELCNT1 register,

CRC01 register,

TOC01 register

Note

,

CR010, CR011 registers,

port setting

Initial setting of these

registers is performed

before setting the

TMC013 and TMC012

bits.

Starts count operation

START

<1> Count operation start flow

TMC013, TMC012 bits = 00

The counter is initialized

and counting is stopped

by clearing the TMC013

and TMC012 bits to 00.

STOP

<2> Count operation stop flow

N + 1

N + 1

M + 1

M + 1

M + 1

Note

Care must be exercised when setting the TOC01 register. For details, refer to

7.3 (3) 16-bit timer

output control register 01 (TOC01)

.

Remark

PPG pulse cycle = (M + 1)

×

Count clock cycle

PPG duty = (N + 1)/(M + 1)