CHAPTER 17 INTERRUPT/EXCEPTION PROCESSING FUNCTION

User’s Manual U16896EJ2V0UD

538

17.2.2 Restore

Execution is restored from non-maskable interrupt servicing by the RETI instruction.

(1) In case of NMI

Restore from NMI processing is done with the RETI instruction.

When the RETI instruction is executed, the CPU performs the following processing and transfers control to the

address of the restored PC.

(i) Loads the values of the restored PC and PSW from FEPC and FEPSW, respectively, because the

PSW.EP bit and the PSW.NP bit are 0 and 1, respectively.

(ii) Transfers control back to the loaded address of the restored PC and PSW.

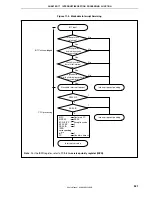

Figure 17-3 shows the processing flow of the RETI instruction.

Figure 17-3. RETI Instruction Processing

PSW.EP

RETI instruction

PC

PSW

EIPC

EIPSW

PSW.NP

Original processing restored

PC

PSW

FEPC

FEPSW

1

1

0

0

Caution When the EP bit and the NP bit are changed by the LDSR instruction during non-maskable

interrupt servicing, in order to restore the PC and PSW correctly during restoring by the RETI

instruction, it is necessary to clear the EP bit back to 0 and set the NP bit back to 1 using the

LDSR instruction immediately before the RETI instruction.

Remark

The solid line shows the CPU processing flow.

(2) In case of INTWDT1, INTWDT2 signals

For non-maskable interrupt servicing by the non-maskable interrupt request signals (INTWDT1, INTWDT2),

refer to

17.10 Cautions

.