CHAPTER 3 CPU FUNCTIONS

User’s Manual U16896EJ2V0UD

48

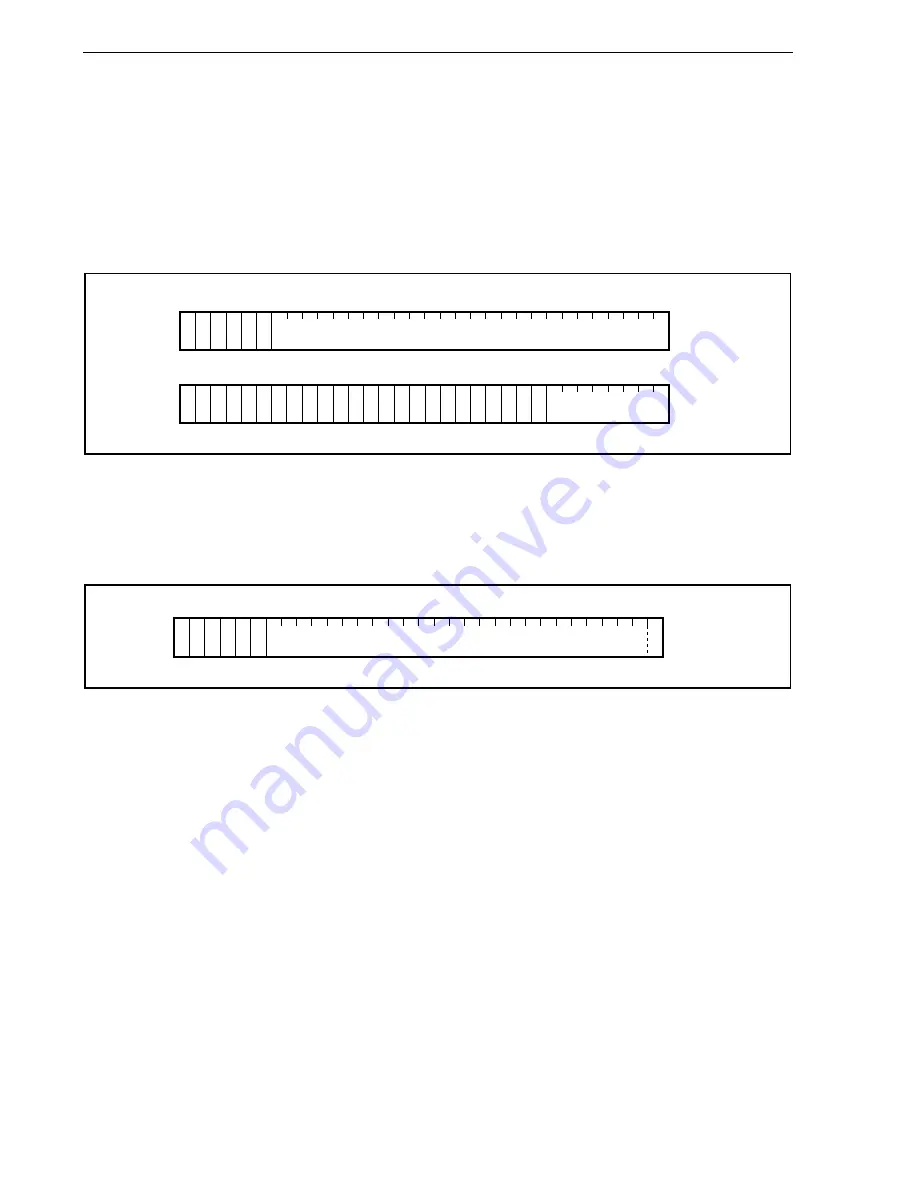

(6) Exception/debug trap status saving registers (DBPC, DBPSW)

There are two exception/debug trap status saving registers, DBPC and DBPSW.

Upon occurrence of an exception trap or debug trap, the contents of the program counter (PC) are saved to

DBPC, and the program status word (PSW) contents are saved to DBPSW.

The contents saved to DBPC consist of the address of the next instruction after the instruction executed when

an exception trap or debug trap occurs.

The current PSW contents are saved to DBPSW.

Bits 31 to 26 of DBPC and bits 31 to 8 of DBPSW are reserved (fixed to 0) for future function expansion.

31

0

DBPC

(PC contents saved)

0

0

After reset

0xxxxxxxH

(x: Undefined)

26 25

0 0 0 0

31

0

DBPSW

(PSW contents saved)

0

0

After reset

000000xxH

(x: Undefined)

8

0 0 0 0

0

0

0 0 0 0

0

0

0 0 0 0

0

0

0 0 0 0

7

(7) CALLT base pointer (CTBP)

The CALLT base pointer (CTBP) is used to specify table addresses and generate target addresses (bit 0 is

fixed to 0).

Bits 31 to 26 are reserved (fixed to 0) for future function expansion.

31

0

CTBP

(Base address)

0

0

After reset

0xxxxxxxH

(x: Undefined)

26 25

0 0 0 0

0