CHAPTER 14 ASYNCHRONOUS SERIAL INTERFACE (UART)

User’s Manual U16896EJ2V0UD

399

(2/2)

RXEn

Reception enable/disable

0

Disable reception

Note

1

Enable reception

•

Set the RXEn bit to 1 after setting the UARTEn bit to 1 at startup. Clear the UARTEn bit to 0 after clearing the

RXEn bit to 0 to stop.

•

To initialize the reception unit status, clear (0) the RXEn bit, and after letting 2 Clock cycles (base clock) elapse,

set (1) the RXEn bit again. If the RXEn bit is not set again, initialization may not be successful. (For details about

the base clock, refer to

14.6.1 (1) Base clock

.)

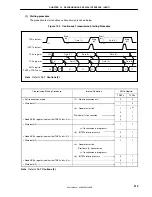

PSn1

PSn0

Transmit operation

Receive operation

0

0

Don’t output parity bit

Receive with no parity

0

1

Output 0 parity

Receive as 0 parity

1

0

Output odd parity

Judge as odd parity

1

1

Output even parity

Judge as even parity

•

To overwrite the PSn1 and PSn0 bits, first clear (0) the TXEn and RXEn bits.

•

If “0 parity” is selected for reception, no parity judgment is performed. Therefore, no error interrupt is generated

because the ASISn.PEn bit is not set.

CLn

Specification of character length of 1 frame of transmit/receive data

0 7

bits

1 8

bits

•

To overwrite the CLn bit, first clear (0) the TXEn and RXEn bits.

SLn

Specification of stop bit length of transmit data

0 1

bit

1 2

bits

•

To overwrite the SLn bit, first clear (0) the TXEn bit.

•

Since reception is always done with a stop bit length of 1, the SLn bit setting does not affect receive operations.

ISRMn

Enable/disable of generation of reception completion interrupt request signals when an error occurs

0

Generate a reception error interrupt request signal (INTSREn) as an interrupt when an error occurs.

In this case, no reception completion interrupt request signal (INTSRn) is generated.

1

Generate a reception completion interrupt request signal (INTSRn) as an interrupt when an error occurs.

In this case, no reception error interrupt request signal (INTSREn) is generated.

•

To overwrite the ISRMn bit, first clear (0) the RXEn bit.

Note

When reception is disabled, the receive shift register does not detect a start bit. No shift-in

processing or transfer processing to the RXBn register is performed, and the contents of the RXBn

register are retained.

When reception is enabled, the receive shift operation starts, synchronized with the detection of the

start bit, and when the reception of one frame is completed, the contents of the receive shift

register are transferred to the RXBn register. A reception completion interrupt request signal

(INTSRn) is also generated in synchronization with the transfer to the RXBn register.