CHAPTER 14 ASYNCHRONOUS SERIAL INTERFACE (UART)

User’s Manual U16896EJ2V0UD

431

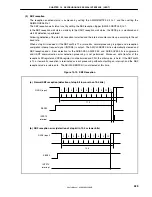

14.6.5 Transfer rate during continuous transmission

During continuous transmission, the transfer rate from a stop bit to the next start bit is extended two clocks of the

base clock longer than normal. However, on the reception side, the transfer result is not affected since the timing is

initialized by the detection of the start bit.

Figure 14-18. Transfer Rate During Continuous Transmission

Start bit

Bit 0

Bit 1

Bit 7

Parity bit

Stop bit

FL

1 data frame

Bit 0

FL

FL

FL

FL

FL

FL

FLstp

Start bit of

second byte

Start bit

Representing the 1-bit data length by FL, the stop bit length by FLstp, and the base clock frequency by f

UCLK

yields the following equation.

FLstp = FL + 2/f

UCLK

Therefore, the transfer rate during continuous transmission is as follows (when the stop bit length = 1).

Transfer rate = 11

×

FL + (2/f

UCLK

)

14.7 Cautions

Cautions to be observed when using UARTn are shown below.

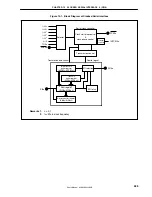

(1) When the supply of clocks to UARTn is stopped (for example, in IDLE or STOP mode), operation stops with

each register retaining the value it had immediately before the supply of clocks was stopped. The TXDn pin

output also holds and outputs the value it had immediately before the supply of clocks was stopped.

However, operation is not guaranteed after the supply of clocks is restarted. Therefore, after the supply of

clocks is restarted, the circuits should be initialized by clearing the ASIMn.UARTEn, ASIMn.RXEn, and

ASIMn.TXEn bits to 000.

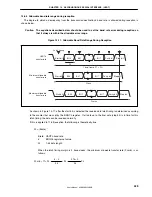

(2) UARTn has a 2-stage buffer configuration consisting of the TXBn register and the transmission shift register,

and has status flags (ASIFn.TXBFn and ASIFn.TXSFn bits) that indicate the status of each buffer. If the

TXBFn and TXSFn bits are read in continuous transmission, the value changes 10

→

11

→

01. For the

timing to write the next data to the TXBn register, read only the TXBFn bit during continuous transmission.