CHAPTER 14 ASYNCHRONOUS SERIAL INTERFACE (UART)

User’s Manual U16896EJ2V0UD

400

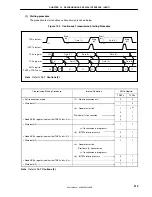

(2) Asynchronous serial interface status register n (ASISn)

The ASISn register, which consists of 3 error flag bits (PEn, FEn, and OVEn), indicates the error status when

UARTn reception is complete.

The ASISn register is cleared to 00H by a read operation. When a reception error occurs, the RXBn register

should be read and the error flag should be cleared after the ASISn register is read.

This register is read-only in 8-bit units.

Reset sets this register to 00H.

Cautions 1. When the ASIMn.UARTEn bit or ASIMn.RXEn bit is cleared to 0, or when the ASISn

register is read, the PEn, FEn, and OVEn bits are cleared (0).

2. Operation using a bit manipulation instruction is prohibited.

3. Accessing the ASISn register is prohibited in the following statuses. For details, refer

to 3.4.8 (1) (b) Access to special on-chip peripheral I/O register.

•

When the CPU operates on the subclock and the main clock oscillation is stopped

•

When the CPU operates on the internal oscillation clock

7

0

ASISn

(n = 0, 1)

6

0

5

0

4

0

3

0

2

PEn

1

FEn

0

OVEn

After reset: 00H R Address: ASIS0 FFFFFA03H, ASIS1 FFFFFA13H

PEn

Status flag indicating a parity error

0

When the UARTEn or RXEn bit is cleared to 0, or after the ASISn register has been read

1

When reception was completed, the receive data parity did not match the parity bit

•

The operation of the PEn bit differs according to the settings of the ASIMn.PSn1 and ASIMn.PSn0 bits.

FEn

Status flag indicating framing error

0

When the UARTEn or RXEn bit is cleared to 0, or after the ASISn register has been read

1

When reception was completed, no stop bit was detected

•

For receive data stop bits, only the first bit is checked regardless of the stop bit length.

OVEn

Status flag indicating an overrun error

0

When the UARTEn or RXEn bit is cleared to 0, or after the ASISn register has been read

1

When UARTn completed the next receive operation before reading receive data of the RXBn register

•

When an overrun error occurs, the next receive data value is not written to the RXBn register and the data is

discarded.

<R>