CHAPTER 8 8-BIT TIMER/EVENT COUNTER 5

User’s Manual U16896EJ2V0UD

308

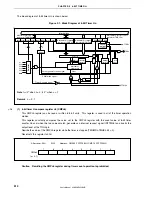

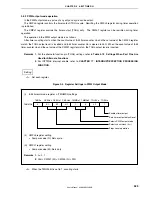

8.4.5 Operation as interval timer (16 bits)

The 16-bit resolution timer/event counter mode is selected by setting the TMC51.TMC514 bit to 1.

8-bit timer/event counter 5n operates as an interval timer by repeatedly generating interrupts using the count value

preset in 16-bit timer compare register 5 (CR5) as the interval.

Setting method

<1> Set each register.

•

TCL50 register:

Selects the count clock (t)

(The TCL51 register does not need to be set in cascade connection)

•

CR50 register:

Compare value (N) ... Lower 8 bits (settable from 00H to FFH)

•

CR51 register:

Compare value (N) ... Higher 8 bits (settable from 00H to FFH)

•

TMC50, TMC51 registers: Selects the mode in which clear & start occurs on a match between TM5

register and CR5 register (

×

: don’t care)

TMC50 register = 0000xx00B

TMC51 register = 0001xx00B

<2> Set the TMC51.TCE51 bit to 1. Then set the TMC50.TCE50 bit to 1 to start the count operation.

<3> When the values of the TM5 register and CR5 register connected in cascade match, the INTTM50 signal

is generated (the TM5 register is cleared to 0000H).

<4> The INTTM50 signal is then generated repeatedly at the same interval.

Interval time = (N + 1)

×

t: N = 0000H to FFFFH

Cautions 1. To write using 8-bit access during cascade connection, set the TCE51 bit to 1 at

operation start and then set the TCE50 bit to 1. When operation is stopped, clear the

TCE50 bit to 0 and then clear the TCE51 bit to 0.

2. During cascade connection, TI50 pin input, TO50 pin output, and the INTTM50 signal

are used. Do not use TI51 pin input, TO51 pin output, and the INTTM51 signal; mask

them instead (for details, refer to CHAPTER 17 INTERRUPT/EXCEPTION

PROCESSING FUNCTION). Clear the LVS51, LVR51, TMC511, and TOE51 bits to 0.

3. Do not change the value of the CR5 register during timer operation.