CHAPTER 28 ELECTRICAL SPECIFICATIONS

User’s Manual U16896EJ2V0UD

669

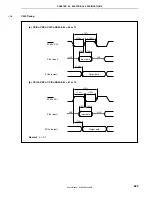

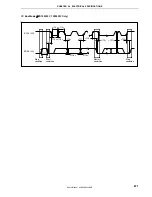

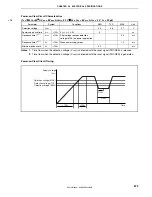

CSI0 Timing

(a) CSICn.CKPn, CSICn.DAPn bits = 00 or 11

SO0n (output)

Input data

Output data

SI0n (input)

SCK0n (I/O)

<101>

<102>

<102>

<103>

<104>

<105>

Hi-Z

Hi-Z

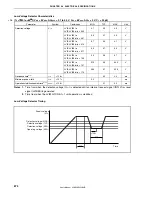

(b) CSICn.CKPn, CSICn.DAPn bits = 01 or 10

SO0n (output)

Input data

Output data

SI0n (input)

SCK0n (I/O)

<101>

<102>

<102>

<103>

<104>

<105>

Hi-Z

Hi-Z

Remark

n = 0, 1

<R>