CHAPTER 19 STANDBY FUNCTION

User’s Manual U16896EJ2V0UD

583

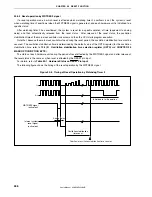

(2) Releasing STOP mode by reset

The same operation as the normal reset operation is performed.

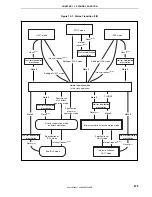

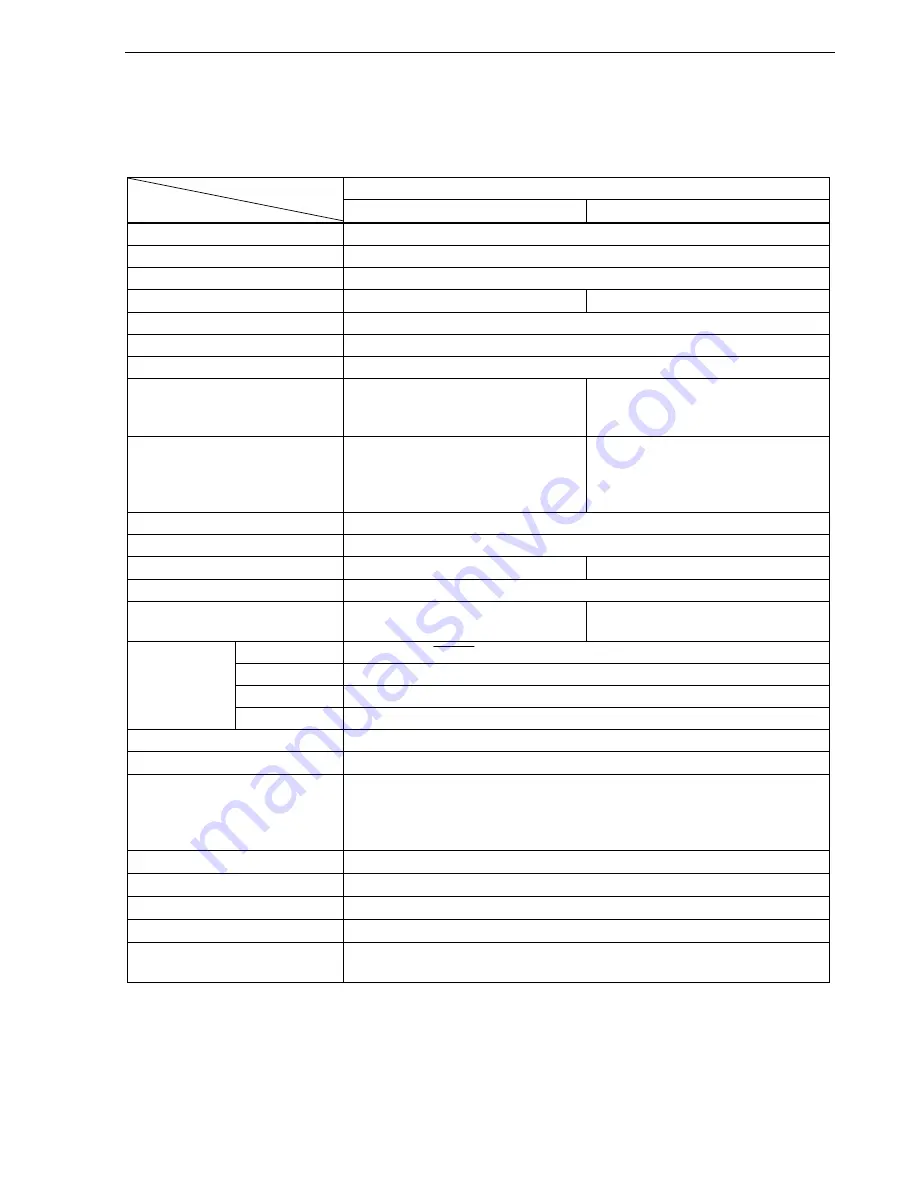

Table 19-7. Operation Status in STOP Mode

When CPU Is Operating with Main Clock

Setting of STOP Mode

Item

When Subclock Is Not Used

When Subclock Is Used

CPU Stops

operation

ROM correction

Stops operation

Main clock oscillator

Oscillation stops

Subclock oscillator

−

Oscillation enabled

Internal oscillator (f

R

) Operable

Interrupt controller

Stops operation

16-bit timer (TMP0)

Stops operation

16-bit timer (TM01)

Stops operation

Operable when INTWT is selected as

count clock and f

XT

is selected as count

clock of WT

8-bit timers (TM50, TM51)

Operable when TI5m is selected as count

clock

Operable when TI5m is selected as count

clock or when INTTM010 is selected as

count clock and TM01 is enabled in STOP

mode

Timer H (TMH0)

Stops operation

Timer H (TMH1)

Operable when f

R

/2048 is selected as count clock

Watch timer

Stops operation

Operable when f

XT

is selected as count clock

Watchdog timer 1

Stops operation

Watchdog timer 2

Operable when f

R

/8 is selected as count

clock

Operable

CSI00, CSI01

Operable when SCK0m input clock is selected as operation clock

I

2

C0

Note 1

Stops

operation

UART0

Operable when ASCK0 is selected as count clock

Serial interface

UART1 Stops

operation

Key interrupt function

Operable

A/D converter

Stops operation

Note 2

Real-time output

Operable when INTTM5m is selected as real-time output trigger and TM5m is enabled in

STOP mode.

However, the RTBH0 and RTBL0 registers cannot be updated because the CPU is

stopped.

Clock monitor (CLM)

Stops operation

Power-on-clear (POC)

Operable

Low-voltage detection (LVI)

Operable

Port function

Retains status before STOP mode was set.

Internal data

The CPU registers, statuses, data, and all other internal data such as the contents of the

internal RAM are retained as they were before the STOP mode was set.

Notes 1.

Only in the

μ

PD703302Y, 70F3302Y

2.

Set the ADM.ADCS and ADM.ADCS2 bits to 00B.

Remark

m = 0, 1

<R>

<R>