CHAPTER 1 INTRODUCTION

User’s Manual U16896EJ2V0UD

27

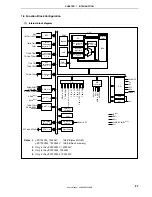

1.6 Function Block Configuration

(1) Internal block diagram

NMI

TO01

TI010, TI011

SO00, SO01

SI00, SI01

SCK00, SCK01

INTP0 to INTP7

INTC

TOP00, TOP01

TIP00, TIP01

TO50, TO51

TI50, TI51

TOH0, TOH1

TXD0, TXD1

RXD0, RXD1

ASCK0

RTP00 to RTP05

KR0 to KR7

RTO: 1 ch

SDA0

Note 2

SCL0

Note 2

CLM

Internal

oscillator

RAM

ROM

PC

ALU

CPU

PDL0 to PDL7

PCM0, PCM1

P90, P91, P96 to P99, P913 to P915

P70 to P77

P50 to P55

P40 to P42

P30 to P35, P38, P39

P00 to P06

AV

REF0

AV

SS

ANI0 to ANI7

ADTRG

IC

Note 3

EV

DD

EV

SS

FLMD0, FLMD1

Note 4

V

SS

BCU

POC

LVI

CG

CLKOUT

X1

X2

XT1

XT2

RESET

V

DD

16-bit

timer/event

counter 0: 1 ch

16-bit timer/

event counter

P: 1 ch

8-bit

timer/event

counter 5: 2 ch

8-bit timer H:

2 ch

Note 1

4 KB

ROM

correction

General-purpose

registers

32 bits

×

32

System

registers

32-bit barrel

shifter

Multiplier

16

×

16

→

32

Instruction

queue

UART: 2 ch

I

2

C

Note 2

:

1 ch

CSI0: 2 ch

Watchdog

timer: 2 ch

Key interrupt

function

Watch timer

Port

A/D

converter

Notes 1.

μ

PD703302, 703302Y:

128 KB (mask ROM)

μ

PD70F3302, 70F3302Y: 128 KB (flash memory)

2.

Only in the

μ

PD703302Y, 70F3302Y

3.

Only in the

μ

PD703302, 703302Y

4.

Only in the

μ

PD70F3302, 70F3302Y