CHAPTER 9 8-BIT TIMER H

User’s Manual U16896EJ2V0UD

320

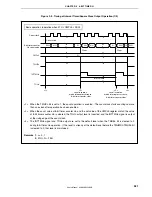

9.4 Operation

9.4.1 Operation as interval timer/square wave output

When the count value of 8-bit timer counter Hn and the set value of the CMPn0 register match, an interrupt request

signal (INTTMHn) is generated and 8-bit timer counter Hn is cleared to 00H.

The CMPn1 register cannot be used in the interval timer mode. Even if the CMPn1 register is set, this has no

effect on the timer output because matches between 8-bit timer counter Hn and the CMPn1 register are not detected.

A square wave of the desired frequency (duty = 50%) is output from the TOHn pin, by setting the TMHMDn.TOENn

bit to 1.

Remarks 1.

For the alternate-function pin (TOHn) settings, refer to

Table 4-12 Settings When Port Pins Are

Used for Alternate Functions

.

2.

For INTTMHn interrupt enable, refer to

CHAPTER 17 INTERRUPT/EXCEPTION PROCESSING

FUNCTION

.

Setting

<1> Set each register.

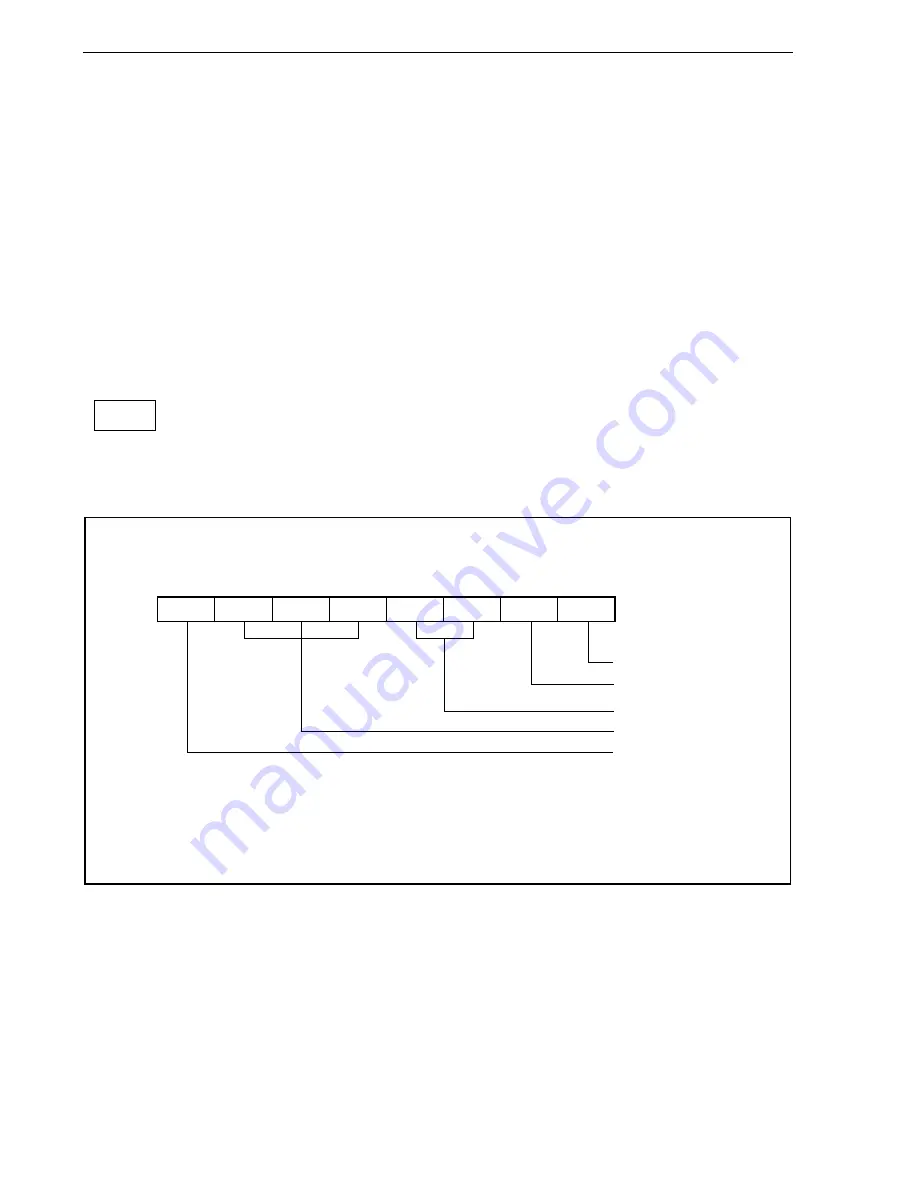

Figure 9-2. Register Settings in Interval Timer Mode

(i) 8-bit timer H mode register n (TMHMDn) settings

0

0/1

0/1

0/1

0

Sets timer output

Sets timer output default level

Sets interval timer mode

Selects count clock (f

CNT

)

Stops count operation

0

0/1

0/1

TMMDn0 TOLEVn

TOENn

CKSHn1

CKSHn2

TMHEn

TMHMDn

CKSHn0 TMMDn1

(ii) CMPn0 register settings

The interval time is as follows if N is set as a comparison value.

•

Interval time = (N + 1)/f

CNT

<2> When the TMHEn bit is set to 1, counting starts.

<3> When the count value of 8-bit timer counter Hn and the set value of the CMPn0 register match, the

INTTMHn signal is generated and 8-bit timer counter Hn is cleared to 00H.

<4> Then, the INTTMHn signal is generated in the same interval. To stop the count operation, clear the TMHEn

bit to 0.