CHAPTER 3 CPU FUNCTIONS

User’s Manual U16896EJ2V0UD

67

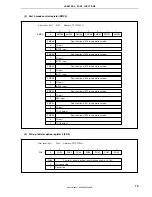

(3) System status register (SYS)

This register is allocated with status flags showing the operating state of the entire system.

This register can be read or written in 8-bit or 1-bit units.

0

Protection error has not occurred

Protection error has occurred

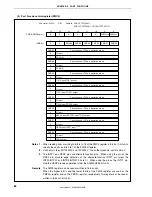

PRERR

0

1

Detection of protection error

SYS

0

0

0

0

0

0

PRERR

After reset: 00H R/W Address: FFFFF802H

< >

The operation conditions of the PRERR flag are described below.

(a) Set conditions (PRERR = 1)

(i) When a write operation to the special register takes place without write operation being performed to

the PRCMD register (when step <3> is performed without performing step <2> as described in

3.4.7

(1) Setting data to special registers

).

(ii) When a write operation (including bit manipulation instruction) to an on-chip peripheral I/O register

other than a special register is performed following write to the PRCMD register (when <3> in

3.4.7

(1) Setting data to special registers

is not a special register).

Remark

Regarding the special registers other than the WDTM register (PCC and PSC registers), even if

on-chip peripheral I/O register read (except bit manipulation instruction) (internal RAM access,

etc.) is performed in between write to the PRCMD register and write to a special register, the

PRERR flag is not set and setting data can be written to the special register.

(b) Clear conditions (PRERR = 0)

(i) When 0 is written to the PRERR flag

(ii) When system reset is performed

Cautions 1. If 0 is written to the PRERR bit of the SYS register that is not a special register

immediately following write to the PRCMD register, the PRERR bit becomes 0 (write

priority).

2. If data is written to the PRCMD register that is not a special register immediately

following write to the PRCMD register, the PRERR bit becomes 1.