CHAPTER 6 16-BIT TIMER/EVENT COUNTER P (TMP)

User’s Manual U16896EJ2V0UD

161

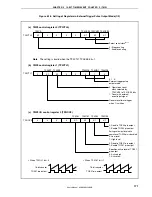

6.5.2 External event count mode (TP0MD2 to TP0MD0 bits = 001)

In the external event count mode, the valid edge of the external event count input is counted when the

TP0CTL0.TP0CE bit is set to 1, and an interrupt request signal (INTTP0CC0) is generated each time the specified

number of edges have been counted. The timer output (TOP00, TOP01 pins) cannot be used.

Usually, the TP0CCR1 register is not used in the external event count mode.

Figure 6-9. Configuration in External Event Count Mode

16-bit counter

CCR0 buffer register

TP0CE bit

TP0CCR0 register

Edge

detector

Clear

Match signal

INTTP0CC0 signal

TIP00 pin

(external event

count input)

Figure 6-10. Basic Timing in External Event Count Mode

FFFFH

16-bit counter

0000H

TP0CE bit

TP0CCR0 register

INTTP0CC0 signal

D

0

D

0

D

0

D

0

16-bit counter

TP0CCR0 register

INTTP0CC0 signal

External event

count input

(TIP00 pin input)

D

0

External

event

count

interval

(D

0

+ 1)

D

0

−

1

D

0

0000

0001

External

event

count

interval

(D

0

+ 1)

External

event

count

interval

(D

0

+ 1)

Remark

This figure shows the basic timing when the rising edge is specified as the valid edge of the

external event count input.

<R>