CHAPTER 20 RESET FUNCTION

User’s Manual U16896EJ2V0UD

590

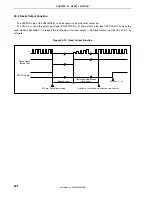

20.3 Register to Check Reset Source

(1) Reset source flag register (RESF)

The RESF register is a special register that can be written only by a combination of specific sequences (refer

to

3.4.7 Special registers

).

The RESF register indicates the source from which a reset signal is generated.

This register can be read or written in 8-bit or 1-bit units (however, only “0” can be written to this register).

RESET pin input or reset by the POC circuit (POCRES) clears this register to 00H. The default value differs if

reset is effected from a source other than the RESET pin.

WDT1RF

WDT2RF

0

1

Not generated

Generated

RESF

0

0

WDT2RF

0

0

CLMRF

LVIRF

After reset:

00H

Note

R/W Address: FFFFF888H

Reset signal from watchdog timer 2 (WDTRES2)

WDT1RF

0

1

Not generated

Generated

Reset signal from watchdog timer 1 (WDTRES1)

LVIRF

0

1

Not generated

Generated

Reset signal from low-voltage detector (LVIRES)

CLMRF

0

1

Not generated

Generated

Reset signal from clock monitor (CLMRES)

Note

This register is cleared to 00H when a reset is executed via the RESET pin or POC circuit.

When a reset is executed by the WDTRES1 signal, WDTRES2 signal, low-voltage detector (LVI), or

clock monitor (CLM), the reset flags of this register (WDT1RF, WDT2RF, CLMRF, and LVIRF bits) are

set (with the other sources retained).

Caution Only “0” can be written to each bit of this register. If writing “0” conflicts with setting the flag

(occurrence of reset), setting the flag takes precedence.