CHAPTER 9 8-BIT TIMER H

User’s Manual U16896EJ2V0UD

321

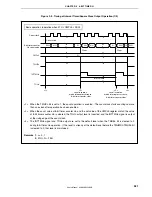

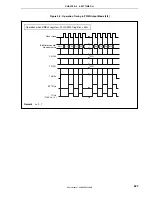

Figure 9-3. Timing of Interval Timer/Square Wave Output Operation (1/2)

Basic operation (operation when 01H

≤

CMPn0

≤

FEH)

00H

Count clock

Count start

8-bit timer counter

Hn count value

CMPn0

TMHEn

INTTMHn

TOHn

01H

N

Clear

Clear

N

00H

01H

N

00H

01H 00H

<1>

<2>

Level inversion,

match interrupt occurrence,

8-bit timer counter clear

<2>

Level inversion,

match interrupt occurrence,

8-bit timer counter clear

<3>

Interval time

<1> When the TMHEn bit is set to 1, the count operation is enabled. The count clock starts counting no more

than one clock after operation has been enabled.

<2> When the count value of 8-bit timer counter Hn and the set value of the CMPn0 register match, the value

of 8-bit timer counter Hn is cleared, the TOHn output level is inverted, and the INTTMHn signal is output

at the rising edge of the count clock.

<3> The INTTMHn signal and TOHn output are set to the default level when the TMHEn bit is cleared to 0

during 8-bit timer Hn operation. If the level is already at the default level before the TMHMDn.TMHEn bit

is cleared to 0, that level is maintained.

Remarks

1.

n = 0, 1

2.

01H

≤

N

≤

FEH