CHAPTER 3 CPU FUNCTIONS

User’s Manual U16896EJ2V0UD

70

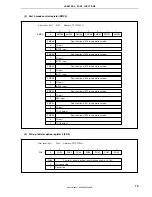

(2) Restriction on conflict between sld instruction and interrupt request

(a) Description

If a conflict occurs between the decode operation of an instruction in <2> immediately before the sld

instruction following an instruction in <1> and an interrupt request before the instruction in <1> is complete,

the execution result of the instruction in <1> may not be stored in a register.

Instruction <1>

•

ld instruction:

ld.b, ld.h, ld.w, ld.bu, ld.hu

•

sld instruction:

sld.b, sld.h, sld.w, sld.bu, sld.hu

•

Multiplication instruction: mul, mulh, mulhi, mulu

Instruction <2>

mov reg1, reg2

satadd reg1, reg2

and reg1, reg2

add reg1, reg2

mulh reg1, reg2

not reg1, reg2

satadd imm5, reg2

tst reg1, reg2

add imm5, reg2

shr imm5, reg2

satsubr reg1, reg2

or reg1, reg2

subr reg1, reg2

cmp reg1, reg2

sar imm5, reg2

satsub reg1, reg2

xor reg1, reg2

sub reg1, reg2

cmp imm5, reg2

shl imm5, reg2

<Example>

<i> ld.w [r11], r10

If the decode operation of the mov instruction <ii> immediately before the sld

instruction <iii> and an interrupt request conflict before execution of the ld

instruction <i> is complete, the execution result of instruction <i> may not be

stored in a register.

<ii> mov r10, r28

<iii> sld.w 0x28, r10

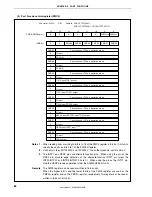

(b) Countermeasure

<1> When compiler (CA850) is used

Use CA850 Ver. 2.61 or later because generation of the corresponding instruction sequence can be

automatically suppressed.

<2> Countermeasure by assembler

When executing the sld instruction immediately after instruction <ii>, avoid the above operation

using either of the following methods.

•

Insert a nop instruction immediately before the sld instruction.

•

Do not use the same register as the sld instruction destination register in the above instruction

<ii> executed immediately before the sld instruction.

•

•

•

<R>