Chapter 24 Usage Notes

24-1

24. Usage

Notes

24.1 Limitation on DMA Data Chaining

•

Overview

The DMA Controller works incorrectly if the DMCCRn.IMMCHN bit is cleared and the address

increment value (DMSAIRn/DMDAIRn) is negative. The DMA Controller might also work

incorrectly regardless of the setting of the DMCCRn.IMMCHN bit if a dynamic or typical DMA

chaining is performed after completion of a transfer with a negative address increment.

•

Symptom

The DMA Controller might read wrong data or write data to wrong addresses.

•

Workaround Measure

Keep the DMCCRn.IMMCHN bit set. Make sure the DMSAIRn and DMDAIRn values for the

last descriptor are equal to or greater than 0 before adding the next command descriptor chain for

dynamic DMA chaining. For DMA data chaining with a negative address increment, write 0 or a

positive number once, then the desired negative increment value to the DMSAIRn/DMDAIRn.

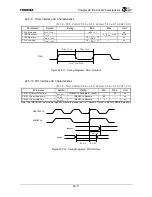

24.2 Limitation on a Register Read After an SIO Software Reset

•

Overview

Immediately reading a register after a software reset (seting “1” to bit 15 of the SIFCRx

Register) results in the SIO not responding and the bus locking up.

•

Symptom

After a software reset (setting “1” to bit 15 of the SIFCRx Register), IMBUSCLK resets SIO for

four clock cycles. During this reset, the SIO does not recognize that it has been accessed even

when it has been accessed. The bus locks up since the device that accesses the SIO waits for a

response from the SIO. A bus error will then be issued if timeout errors have been enabled.

•

Workaround Measure

After the software reset, perform a dummy read operation to the register of a different module

on the IM-Bus, then access the SIO register. Performing the dummy access on the IM-Bus requires

eight IMBUSCLK cycles to complete, making it possible to avoid the problem since this is longer

than the amount of time the SIO reset requires.

24.3 Other

Precautions

•

Always set bit 4 in the G-Bus Arbiter Control register (GARBC) to 1. Clearing this bit might cause

arbitration deadlocks.

•

There are restrictions for address increment values regarding DMA burst transfers. For a detailed

description, see Section 8.3.7, “Single Address Transfer,” and Section 8.3.8, “Dual Address

Transfer.”

•

The four target address spaces (MEM0, MEM1, MEM2 and IO) of the PCI Controller may not

overlap. See Section 10.3.5, “Target Access.”

•

It is recommended to set the G2P Timeout register (GPTOCNT) to 0. See Section 10.4.12, “G2P

Timeout Count Register.”

Содержание TMPR4925

Страница 1: ...64 Bit TX System RISC TX49 Family TMPR4925 Rev 3 0 ...

Страница 4: ......

Страница 15: ...Handling Precautions ...

Страница 16: ......

Страница 18: ...1 Using Toshiba Semiconductors Safely 1 2 ...

Страница 40: ...3 General Safety Precautions and Usage Considerations 3 18 ...

Страница 42: ...4 Precautions and Usage Considerations 4 2 ...

Страница 43: ...TMPR4925 ...

Страница 44: ......

Страница 54: ...Chapter 1 Features 1 8 ...

Страница 58: ...Chapter 2 Block Diagram 2 4 ...

Страница 88: ...Chapter 4 Address Mapping 4 12 ...

Страница 226: ...Chapter 8 DMA Controller 8 58 ...

Страница 260: ...Chapter 9 SDRAM Controller 9 34 ...

Страница 480: ...Chapter 15 Interrupt Controller 15 32 ...

Страница 554: ...Chapter 19 Real Time Clock RTC 19 8 ...

Страница 555: ...Chapter 20 Removed 20 1 20 Removed ...

Страница 556: ...Chapter 20 Removed 20 2 ...

Страница 564: ...Chapter 21 Extended EJTAG Interface 21 8 ...

Страница 580: ...Chapter 22 Electrical Characteristics 22 16 ...

Страница 586: ...Chapter 23 Pin Layout Package 23 6 23 2 Package Package Type Package Code 256 pin PBGA PBGA 4L P BGA256 2727 1 27A4 ...

Страница 588: ...Chapter 24 Usage Notes 24 2 ...

Страница 590: ...Appendix A TX49 H2 Core Supplement A 2 ...