Chapter 10 PCI Controller

10-37

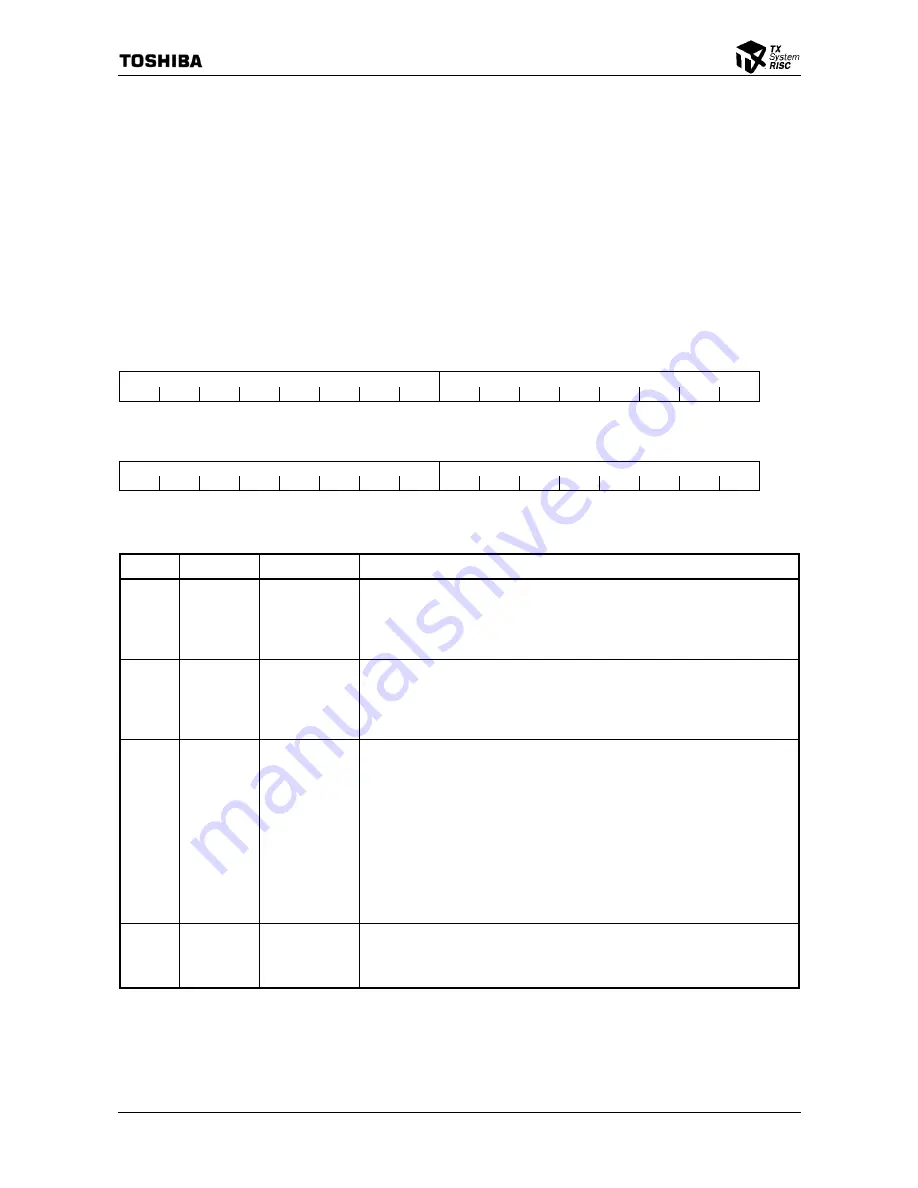

10.4.11 PCI Configuration 2 Register (PCICFG2)

0xD03C

The following fields correspond to the following registers:

Max. Latency field

→

Max_Lat Register of the PCI Configuration Space

Min.

Grant

field

→

Min_Gnt Register of the PCI Configuration Space

Interrupt Pin field

→

Interrupt Pin Register of the PCI Configuration Space

Interrupt Line field

→

Interrupt Line Register of the PCI Configuration Space.

A write to Register PCICDATA3 when PCICCFG.LCFG=1 will modify the contents of this register.

Otherwise this register is Read Only.

This register cannot be accessed when the PCI Controller is in the Satellite mode.

31

24

23

16

ML MG

R/L R/L

:

Type

0x00

0x00

: Initial value

15

8

7 0

IP IL

R/L R/W

:

Type

0x00

0x00

: Initial value

Bits Mnemonic Field

Name

Description

31:24 ML

Maximum

Latency

Max_Lat (Maximum Latency) (Initial value: 0x00, R/L)

00h: Does not use this register to determine PCI Bus priority.

01h-FFh: Specifies the time interval for requesting bus ownership.

In units of 250 ns, assuming the PCICLK is 33 MHz.

It is possible to change the maximum latency by software.

23:16

MG

Minimum Grant

Min_Gnt (Minimum Grant) (Initial value: 0x00, R/L)

00h: Is not used to calculate the latency timer value.

01h-FFh: Sets the time required for Burst transfer.

In units of 250 ns, assuming the PCICLK is 33 MHz.

It is possible to change this valuesoftware.

15:8

IP

Interrupt Pin

Interrupt Pin (Initial value: 0x00, R/L)

Valid values: 00 - 04h

00h: Do not use interrupt signals.

01h: Use Interrupt signal INTA

*

02h: Use Interrupt signal INTB

*

03h: Use Interrupt signal INTC

*

04h: Use Interrupt signal INTD

*

05h - FFh: Reserved

It is possible to change this value by software.

When using either the REQ[2]

*

signal or the PIO signal to report an interrupt to an

external device as the PCI device, please use EEPROM to set the connection with

that device.

7:0

IL

Interrupt Line

Interrupt Line (Initial value: 0x00, R/L)

This is a readable/writable 8-bit register. The software uses this register to indicate

information such as the interrupt signal connection information. Operation of the

TX4925 is not affected.

Figure 10.4.11 PCI Configuration 2 Register

Содержание TMPR4925

Страница 1: ...64 Bit TX System RISC TX49 Family TMPR4925 Rev 3 0 ...

Страница 4: ......

Страница 15: ...Handling Precautions ...

Страница 16: ......

Страница 18: ...1 Using Toshiba Semiconductors Safely 1 2 ...

Страница 40: ...3 General Safety Precautions and Usage Considerations 3 18 ...

Страница 42: ...4 Precautions and Usage Considerations 4 2 ...

Страница 43: ...TMPR4925 ...

Страница 44: ......

Страница 54: ...Chapter 1 Features 1 8 ...

Страница 58: ...Chapter 2 Block Diagram 2 4 ...

Страница 88: ...Chapter 4 Address Mapping 4 12 ...

Страница 226: ...Chapter 8 DMA Controller 8 58 ...

Страница 260: ...Chapter 9 SDRAM Controller 9 34 ...

Страница 480: ...Chapter 15 Interrupt Controller 15 32 ...

Страница 554: ...Chapter 19 Real Time Clock RTC 19 8 ...

Страница 555: ...Chapter 20 Removed 20 1 20 Removed ...

Страница 556: ...Chapter 20 Removed 20 2 ...

Страница 564: ...Chapter 21 Extended EJTAG Interface 21 8 ...

Страница 580: ...Chapter 22 Electrical Characteristics 22 16 ...

Страница 586: ...Chapter 23 Pin Layout Package 23 6 23 2 Package Package Type Package Code 256 pin PBGA PBGA 4L P BGA256 2727 1 27A4 ...

Страница 588: ...Chapter 24 Usage Notes 24 2 ...

Страница 590: ...Appendix A TX49 H2 Core Supplement A 2 ...