Chapter 17 Serial Peripheral Interface

17-13

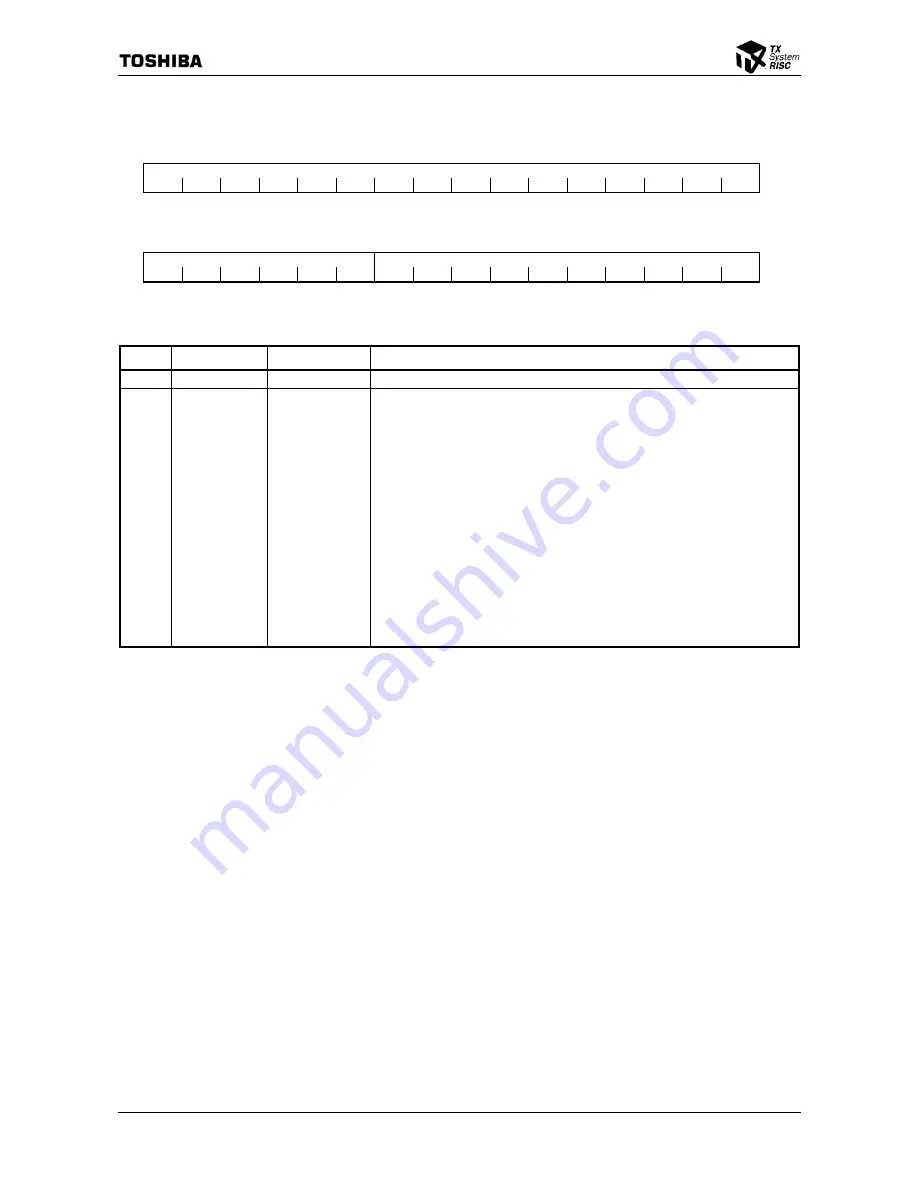

17.4.4 SPI Inter Frame Space Register (SPFS)

0xF80C

31

16

Reserved

: Type

: Initial value

15

10

9 0

Reserved IFS

R/W

:

Type

0000000000

: Initial value

Bits Mnemonic Field

Name

Explanation

31:10

⎯

Reserved

⎯

9:0 IFS

Inter Frame

Space

Inter Frame Space (Initial value: 0000000000b, R/W)

Configure the amount of time, which is inserted between two consecutive frames.

When setting this register to 0, two consecutive transfers will be send using only

minimum amount of time required to load the buffers between consecutive frames.

This minimum amount of time is not zero.

When the prescaler is not used (IFSPSE bit in SPCR0 register is “0”), the inter

frame space can be calculated using the following formula:

f

IFS

= n/f

SEI

(range is 25 ns up to 25.6

µ

s when MASTERCLK frequency is 80 MHz.)

When using the prescaler (IFSPSE bit in SPCR0 register is “1”), the inter frame

space can be calculated using the following formula:

f

IFS

= 32

×

n/f

SEI

(range is 800 ns up to 819.2

µ

s when MASTERCLK frequency is 80 MHz.)

Please write to this register when SIDLE bit is “0”.

Figure 17.4.4 SPI Inter Frame Space Register (SPFS)

Содержание TMPR4925

Страница 1: ...64 Bit TX System RISC TX49 Family TMPR4925 Rev 3 0 ...

Страница 4: ......

Страница 15: ...Handling Precautions ...

Страница 16: ......

Страница 18: ...1 Using Toshiba Semiconductors Safely 1 2 ...

Страница 40: ...3 General Safety Precautions and Usage Considerations 3 18 ...

Страница 42: ...4 Precautions and Usage Considerations 4 2 ...

Страница 43: ...TMPR4925 ...

Страница 44: ......

Страница 54: ...Chapter 1 Features 1 8 ...

Страница 58: ...Chapter 2 Block Diagram 2 4 ...

Страница 88: ...Chapter 4 Address Mapping 4 12 ...

Страница 226: ...Chapter 8 DMA Controller 8 58 ...

Страница 260: ...Chapter 9 SDRAM Controller 9 34 ...

Страница 480: ...Chapter 15 Interrupt Controller 15 32 ...

Страница 554: ...Chapter 19 Real Time Clock RTC 19 8 ...

Страница 555: ...Chapter 20 Removed 20 1 20 Removed ...

Страница 556: ...Chapter 20 Removed 20 2 ...

Страница 564: ...Chapter 21 Extended EJTAG Interface 21 8 ...

Страница 580: ...Chapter 22 Electrical Characteristics 22 16 ...

Страница 586: ...Chapter 23 Pin Layout Package 23 6 23 2 Package Package Type Package Code 256 pin PBGA PBGA 4L P BGA256 2727 1 27A4 ...

Страница 588: ...Chapter 24 Usage Notes 24 2 ...

Страница 590: ...Appendix A TX49 H2 Core Supplement A 2 ...