Chapter 22 Electrical Characteristics

22-5

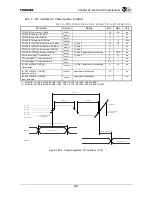

22.5.3 SDRAM Interface AC Characteristics

(Tc = 0 ~ 70

°

C, V

CCIO

= 3.3 V

±

0.3 V, V

CCInt

= 1.5 V

±

0.1 V, V

SS

= 0 V, CL = 50 pF)

Parameter Symbol

Rating

Min.

Max.

Unit

SDCLK[3:0] Cycle Time

t

CYC_SDCLK

12.5

⎯

ns

SDCLK[3:0] High Time

t

HIGH_SDCLK

3

⎯

ns

SDCLK[3:0] Low Time

t

LOW_SDCLK

3

⎯

ns

SDCLKIN Skew

t

BP

Non bypass mode

0

4.0

ns

ADDR[19:16,14:5],SADDR10 Output delay

t

VAL_ADDR1

(

*

1) 1.5

7.5

ns

SDCS[3:0]

*

Output delay

t

VAL_SDCS

1.5

7.5

ns

RAS

*

Output delay

t

VAL_RAS

(

*

1) 1.5

7.5

ns

CAS

*

Output delay

t

VAL_CAS

(

*

3) 1.5

7.5

ns

WE

*

Output delay

t

VAL_WE

(

*

3) 1.5

7.5

ns

CKE Output delay

t

VAL_CKE

1.5

7.5

ns

DQM[3:0] Output delay

t

VAL_DQM

(

*

2) 1.5

7.5

ns

DATA[31:0] Output delay (H->L, L->H)

t

VAL_DATA1

(

*

2) 1.5

7.5

ns

DATA[31:0] Output delay (High-Z->Valid)

t

VAL_DATA1ZV

(

*

2) 1.5

7.5

ns

DATA[31:0] Output delay (Valid->High-Z)

t

VAL_DATA1VZ

(

*

2) 1.5

7.5

ns

DATA[31:0] Input set-up time

t

SU_DATA1B

Bypass mode

6.0

⎯

ns

DATA[31:0] input hold time

t

HO_DATA1B

Bypass

mode

0.5

⎯

ns

DATA[31:0] Input set-up time

t

SU_DATA1NB

Non bypass mode

1.0

⎯

ns

DATA[31:0] input hold time

t

HO_DATA1NB

Non bypass mode

2.0

⎯

ns

*

1: An SDRAM bus transaction can complete in no more than two clock cycles when the SDCTR.DA is set to 1.

*

2: An SDRAM bus transaction can complete in no more than two clock cycles when the SDCTR.SWB is set to 1.

*

3: 2 cycle signals.

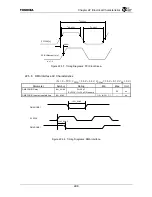

Figure 22.5.3 Timing Diagrams: Output Signals and When Bypass Mode Input Signals (SDCLK Basis)

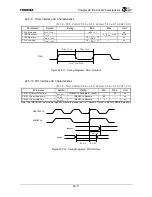

Figure 22.5.4 Timing Diagrams: When Non Bypass Mode Input Signals (SDCLK Basis)

SDCLK[n]

t

SU

_

*

t

HO

_

*

outputs valid

inputs valid

t

VAL_

*

OUTPUT

INPUT

t

SU

_

*

t

HO

_

*

SDCLK[n]

t

BP

inputs valid

SDCLKIN

INPUT

Содержание TMPR4925

Страница 1: ...64 Bit TX System RISC TX49 Family TMPR4925 Rev 3 0 ...

Страница 4: ......

Страница 15: ...Handling Precautions ...

Страница 16: ......

Страница 18: ...1 Using Toshiba Semiconductors Safely 1 2 ...

Страница 40: ...3 General Safety Precautions and Usage Considerations 3 18 ...

Страница 42: ...4 Precautions and Usage Considerations 4 2 ...

Страница 43: ...TMPR4925 ...

Страница 44: ......

Страница 54: ...Chapter 1 Features 1 8 ...

Страница 58: ...Chapter 2 Block Diagram 2 4 ...

Страница 88: ...Chapter 4 Address Mapping 4 12 ...

Страница 226: ...Chapter 8 DMA Controller 8 58 ...

Страница 260: ...Chapter 9 SDRAM Controller 9 34 ...

Страница 480: ...Chapter 15 Interrupt Controller 15 32 ...

Страница 554: ...Chapter 19 Real Time Clock RTC 19 8 ...

Страница 555: ...Chapter 20 Removed 20 1 20 Removed ...

Страница 556: ...Chapter 20 Removed 20 2 ...

Страница 564: ...Chapter 21 Extended EJTAG Interface 21 8 ...

Страница 580: ...Chapter 22 Electrical Characteristics 22 16 ...

Страница 586: ...Chapter 23 Pin Layout Package 23 6 23 2 Package Package Type Package Code 256 pin PBGA PBGA 4L P BGA256 2727 1 27A4 ...

Страница 588: ...Chapter 24 Usage Notes 24 2 ...

Страница 590: ...Appendix A TX49 H2 Core Supplement A 2 ...