Chapter 10 PCI Controller

10-9

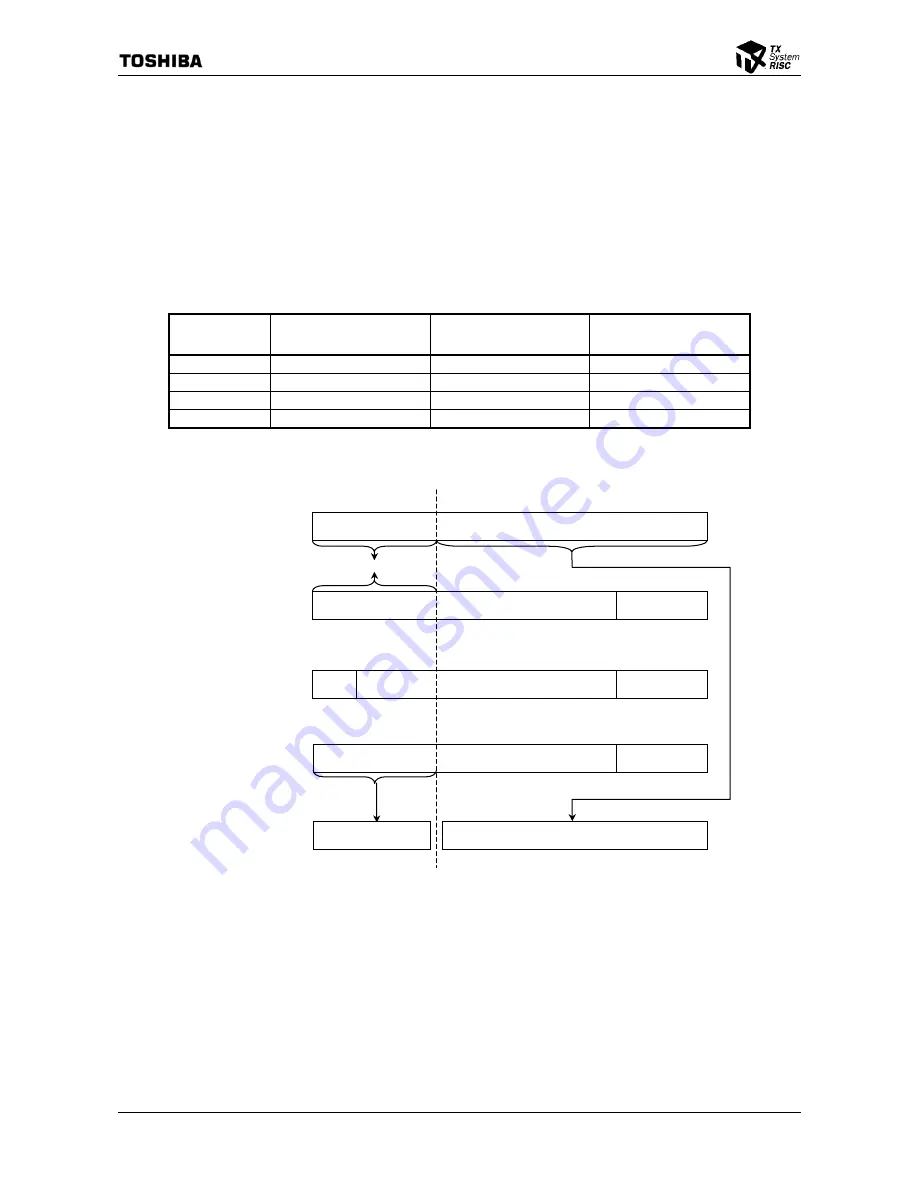

When expressed as a formula, conversion of a G-Bus address (GBusAddr[31:0]) into a PCI Bus

Address (PCIAddr[31:0]) is as follows below. GBASE[31:8], PBASE[31:8], and AM[28:8] each

represent the setting register of the corresponding access window indicated below in Table 10.3.2. The

“&” symbol indicates a logical AND for each bit, “||” indicates a logical OR for each bit, “!” indicates

logical NOT, and “|” indicates bit linking.

If ((GBusAddr[31:29] | (GBusAddr[28:8] & ! AM[28:8] == GBASE[31:29] | (GBASE[28:8] & ! AM[28:8]) then

PCIAddr[31:0] = PBASE[31:29] | ((PBASE[28:8] & ! AM[28:8]) || (GBusAddr[28:8] & AM[28:8]))

| GBusAddr[7:0];

Table 10.3.2 Initiator Access Space Address Mapping Register

G-Bus

Base

Address

GBASE[31:8]

PCI Bus Base Address

PBASE[31:8]

Address Mask

AM[28:8]

Memory Space 0

G2PM0GBASE.BA[31:8]

G2PM0PBASE.BA[31:8]

G2PM0MASK.AM[28:8]

Memory Space 1

G2PM1GBASE.BA[31:8]

G2PM1PBASE.BA[31:8]

G2PM1MASK.AM[28:8]

Memory Space 2

G2PM2GBASE.BA[31:8]

G2PM2PBASE.BA[31:8]

G2PM2MASK.AM[28:8]

I/O Space

G2PIOGBASE.BA[31:8]

G2PIOPBASE.BA[31:8]

G2PIOMASK.AM[28:8]

Figure 10.3.4 illustrates this address conversion.

Figure 10.3.4 Address Conversion For Initiator (G-Bus

→

PCI Bus Address Conversion)

It is possible to set each space to valid/invalid or to perform Word Swap (see “10.3.7 Endian

Switching Function”). Table 10.3.3 shows the settings registers for these properties.

Also, operation is not guaranteed if resources in the PCI space were made cacheable and were then

accessed when the Critical Word First function of the TX49/H2 core was enabled.

GBusAddr

0

31

0x00

0

31

7

8

Compare

GBASE

0x00

0

31

7

8

AM

000 000 - - - - - - - - - - - 0 0 1 1 1 - - - - - - - - - - - - - - -

0x00

0

31

7

8

PBASE

0

31

PCIAddr

29 28

Содержание TMPR4925

Страница 1: ...64 Bit TX System RISC TX49 Family TMPR4925 Rev 3 0 ...

Страница 4: ......

Страница 15: ...Handling Precautions ...

Страница 16: ......

Страница 18: ...1 Using Toshiba Semiconductors Safely 1 2 ...

Страница 40: ...3 General Safety Precautions and Usage Considerations 3 18 ...

Страница 42: ...4 Precautions and Usage Considerations 4 2 ...

Страница 43: ...TMPR4925 ...

Страница 44: ......

Страница 54: ...Chapter 1 Features 1 8 ...

Страница 58: ...Chapter 2 Block Diagram 2 4 ...

Страница 88: ...Chapter 4 Address Mapping 4 12 ...

Страница 226: ...Chapter 8 DMA Controller 8 58 ...

Страница 260: ...Chapter 9 SDRAM Controller 9 34 ...

Страница 480: ...Chapter 15 Interrupt Controller 15 32 ...

Страница 554: ...Chapter 19 Real Time Clock RTC 19 8 ...

Страница 555: ...Chapter 20 Removed 20 1 20 Removed ...

Страница 556: ...Chapter 20 Removed 20 2 ...

Страница 564: ...Chapter 21 Extended EJTAG Interface 21 8 ...

Страница 580: ...Chapter 22 Electrical Characteristics 22 16 ...

Страница 586: ...Chapter 23 Pin Layout Package 23 6 23 2 Package Package Type Package Code 256 pin PBGA PBGA 4L P BGA256 2727 1 27A4 ...

Страница 588: ...Chapter 24 Usage Notes 24 2 ...

Страница 590: ...Appendix A TX49 H2 Core Supplement A 2 ...