MAX32600 User’s Guide

Analog Front End

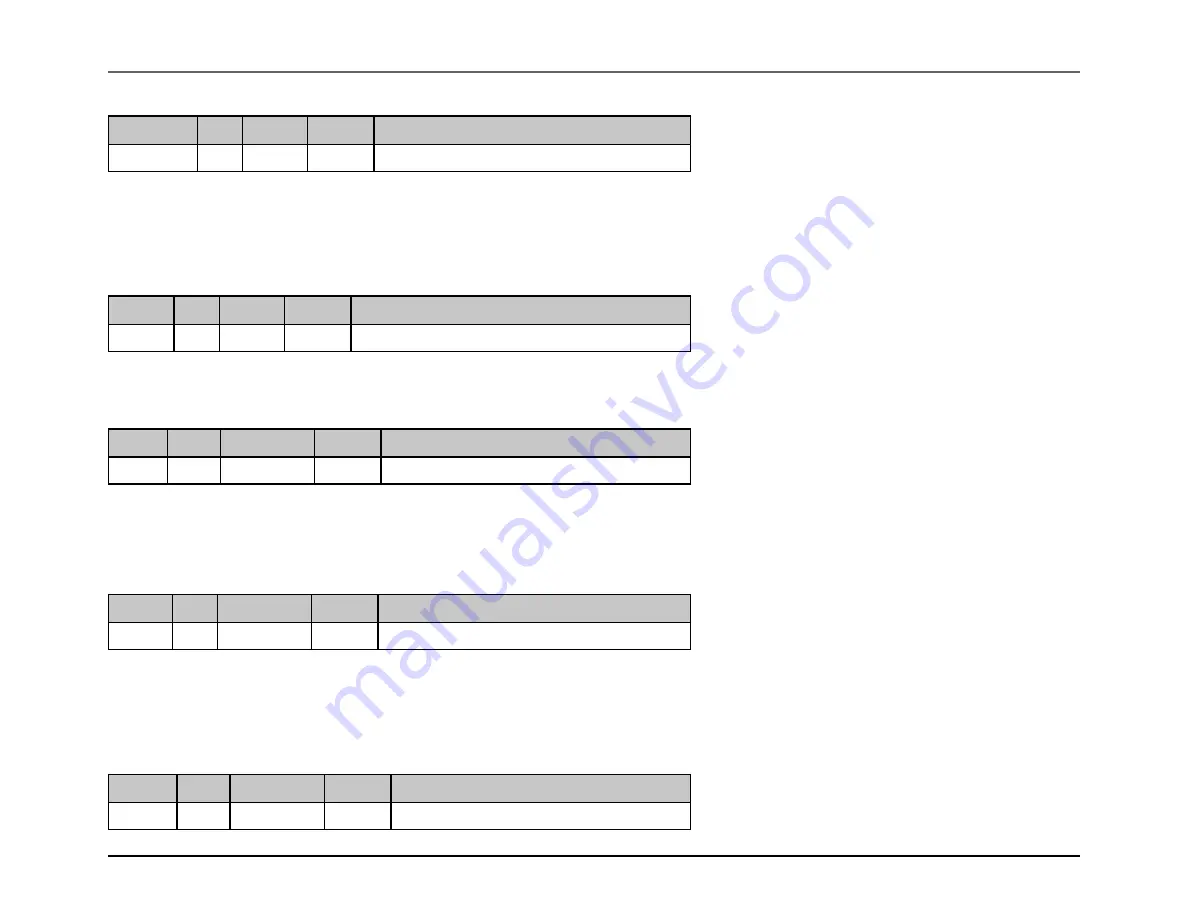

8.3 ADC

Field

Bits

Default

Access

Description

ro_cal_load

2

0

R/W

Load Initial RO Calibration Trim

1: Loads trm_init into factory calibration closed loop.

ADCCFG_RO_CAL0.trm_mu

Field

Bits

Default

Access

Description

trm_mu

19:8

000h

R/W

Auto Calibration Loop Gain

ADCCFG_RO_CAL0.ro_trm

Field

Bits

Default

Access

Description

ro_trm

31:23

000000000b

R/O

Auto Calibration Loop Register Readback

8.3.5.1.12

ADCCFG_RO_CAL1

ADCCFG_RO_CAL1.trm_init

Field

Bits

Default

Access

Description

trm_init

8:0

000000000b

R/W

Initial Setting for RO Trim Calibration

Contains the setting to load to auto calibration register (2’s complement format). Used as an initial condition for the closed loop calibration.

ADCCFG_RO_CAL1.trm_min

Field

Bits

Default

Access

Description

trm_min

18:10

100000000b

R/W

Trim Lower Limit

Rev.1.3 April 2015

Maxim Integrated

Page 450

Содержание MAX32600

Страница 1: ...MAX32600 User s Guide April 2015...