MAX32600 User’s Guide

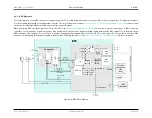

Analog Front End

8.3 ADC

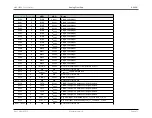

ADC Input Clock Source

01b

PLL 8MHz Output

10b

External High Frequency Clock

11b

24MHz Relaxation Oscillator

Peripheral Clock Mode (Clock Divisor)

The ADC peripheral clock, PCLK, is generated based on the ADC input clock source as set in the previous section. The ADC Peripheral Clock directly clocks the

ADC internally and is based on a divisor of the ADC Input Clock Source Selection. To set PCLK, register field

is used.

PCLK

Notes

000b

PCLK = Input Clock / 1

PLL generates 8MHz clock

001b

PCLK = Input Clock / 2

010b

PCLK = Input Clock / 3

Default State

011b

PCLK = Input Clock / 4

100b

PCLK = Input Clock / 6

101b

PCLK = Input Clock / 8

110b

PCLK = Input Clock / 12

111b

Reserved

Clock Gating

Prior to using the ADC, clock gating must be turned off by setting

to 1. When the ADC is not being used,

should be set to 0 to ensure lowest power operation.

Clock Enable

Once all of the clock settings are set up (and prior to taking a measurement), set

to 1. This enables the ADC clock tree and PCLK

generation.

Rev.1.3 April 2015

Maxim Integrated

Page 408

Содержание MAX32600

Страница 1: ...MAX32600 User s Guide April 2015...