MAX32600 User’s Guide

System Configuration and Management

4.1 Power Ecosystem and Operating Modes

• 10b: 128 clocks

• 11b: 256 clocks

Notes

∗

• This field is reset by any of the following conditions/events:

–

PwrSeq RSTN (power sequencer asynchronous reset)

–

System Reboot event

–

Whenever pwr_prv_pwr_fail_r == 1

–

Whenever pwr_prv_boot_fail_r == 1

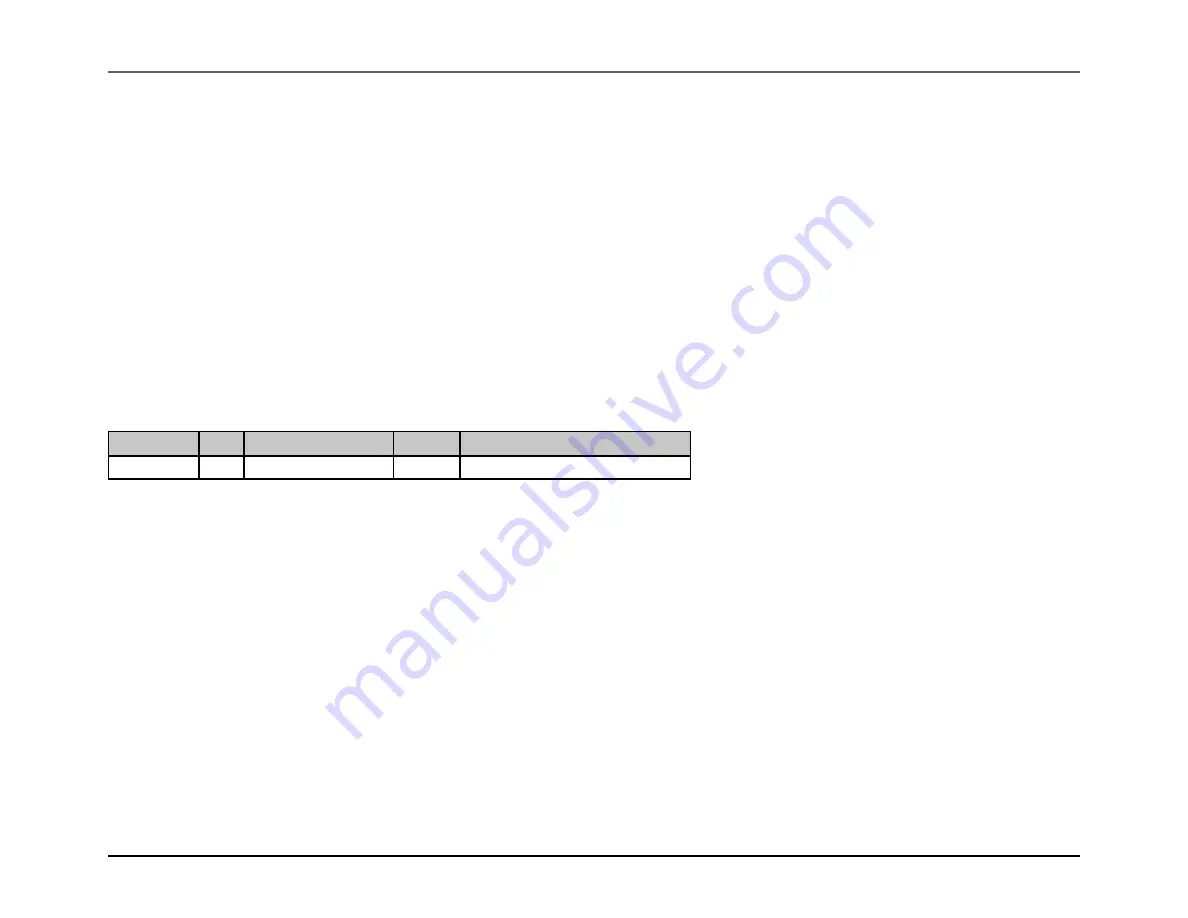

PWRSEQ_REG3.pwr_svmsel

Field

Bits

Default

Access

Description

pwr_svmsel

7:5

000b (PwrSeq RSTN)

R/W

pwr_svmsel_o[2:0]

SVM timeout count. (SVM clks)

• 000 - Bypass (Default)

• 001 - 30 sec

• 010 - 1 min

• 011 - 2 min

• 100 - 4 min

• 101 - 8 min

• 110 - 16 min

• 111 - 32 min.

PWRSEQ_REG3.pwr_pwrfltrsvmselo

Rev.1.3 April 2015

Maxim Integrated

Page 82

Содержание MAX32600

Страница 1: ...MAX32600 User s Guide April 2015...