MAX32600 User’s Guide

System Clock, Timers/Counters, Watchdog Timers and Real Time Clock

10.1 System Clock

Firmware Control of the External 32kHz Clock

The 32kHz RTC clock is enabled with the

bit for

and

bit for

10.1.3.4

Phase Lock Loop

An on-chip Phase Lock Loop (PLL) is provided to allow for generation of a 48MHz USB clock using lower value external quartz crystals or ceramic resonators. The

crystal clock multiplier is controlled via the

register. Note that proper divisor select is required with the different frequencies of the XTAL

reference clocks.

The PLL is selectable between 2X, 4X, and 6X frequency multiplication modes and has a nominal output frequency of 48MHz. Note that the maximum frequency the

CPU can be operated at is 24MHz. The PLL’s 48MHz output is divided down by two in order to be used as a CPU clock source. To select the multiplier for the PLL,

set the

CLKMAN_CLK_CONFIG.pll_divisor_select

bit field appropriately.

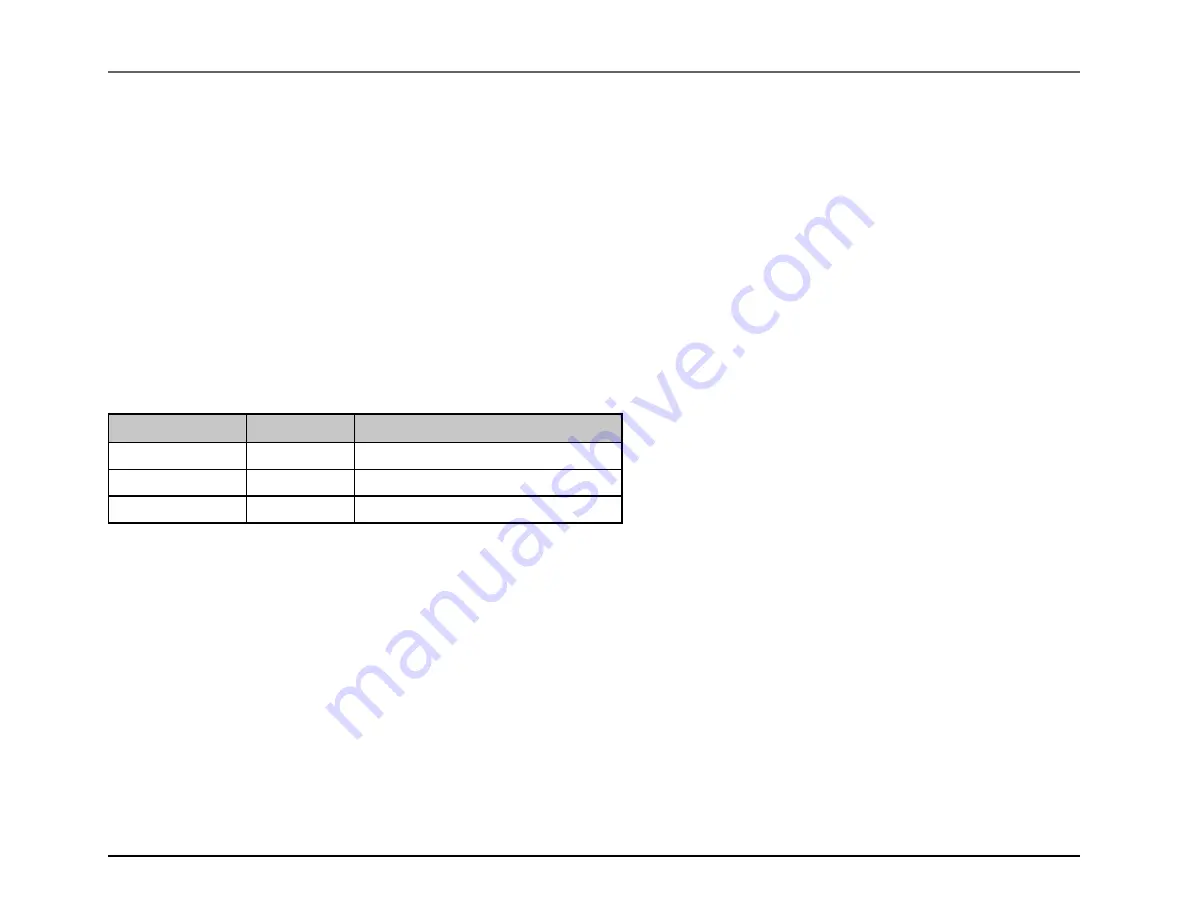

PLL Frequency Divisor Selection

PLL Multiplier

Input Clock Freq (HFXIN / Internal Osc)

00b

2X

24MHz

01b

4X

12MHz

1xb

6X

8MHz

Rev.1.3 April 2015

Maxim Integrated

Page 505

Содержание MAX32600

Страница 1: ...MAX32600 User s Guide April 2015...