MAX32600 User’s Guide

Analog Front End

8.3 ADC

8.3

ADC

8.3.1

ADC Overview

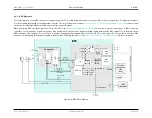

The

MAX32600

features a 16-bit analog-to-digital converter (ADC) with a 16-channel analog input multiplexer as shown in the

below.

This multiplexer selects input from any one of 16 input lines in single-ended mode or two of eight input pairs in differential mode. The differential mode supports fully

differential signal inputs.

The Programmable Gain Amplifier (PGA) allows programmable gain settings of 1X, 2X, 4X, and 8X before the input sample is converted. It also relaxes the input

settling time requirements. Optionally, the PGA can be bypassed so that the multiplexer outputs are passed directly to the ADC to save power.

The

MAX32600

16-bit ADC supports the following features:

• Configurable clock rate

• Sample rate control up to 500ksps

• Single-ended and differential input modes with unipolar and bipolar signal conditioning

–

Bipolar input ranges (

±

V

REF

,

±

V

REF

/2)

–

Unipolar input range (0 to V

REF

)

• Over-sampling and decimation filtering

• Ability to synchronize to DAC waveform generation

• Programmable out of range detection

8.3.2

ADC Architecture

The ADC on the

MAX32600

is a cyclic analog-to-digital converter. This architecture - sometimes referred to as a recycling architecture - does not alter the reference

voltage; rather, any error or residue of the amplifier is doubled. There are certain similarities with a Pipeline ADC: each cycle calculates 1-bit. However, unlike a

Pipeline ADC, the amplified value of the input is summed to a reference voltage and residue voltage from this process is further amplified during each successive

Rev.1.3 April 2015

Maxim Integrated

Page 403

Содержание MAX32600

Страница 1: ...MAX32600 User s Guide April 2015...