MAX32600 User’s Guide

Introduction

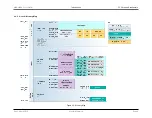

2.5 Memory

2.4.5

Cryptographic Internal Oscillator

To reduce opportunities for timing-based analysis and fault injection (clock interference) attacks targeting the cryptographic and security functions of the device (such

as the AES cryptographic engine, the uMAA, and other related functions), a dedicated on-chip oscillator is provided on the

MAX32600

which can be used to supply

a separate, isolated clock for use by these functions.

Decoupling these functions from the main system clock allows encryption and decryption operations to take a constant amount of time regardless of the current

system clock rate, and also provides a more variable (and not externally observable) clock to reduce the opportunity for an attacker to perform power or timing

analysis attacks against the cryptographic and security functions.

2.5

Memory

2.5.1

Internal Flash Program Memory

The

MAX32600

includes from 64 KB to 256 KB (depending on the specific device production option) of internal flash program memory. Internally, the flash memory

has a width of 64-bits. Flash memory must thus be programmed one 64-bit location at a time, which requires two programming operations of 32-bits each. The flash

is divided into logical pages; when erasing the flash, it is possible to erase either a single page (page erase) or the entire flash array (mass erase) in one operation.

For read access, the program flash memory is mapped into the standard code space region beginning at address 0x0000_0000. Modifying the flash memory array

(either program or erase operations) is handled by the flash controller peripheral.

The flash controller also provides the ability to directly program a flash location by writing a 32-bit value to the proper memory location using the AHB bus (as opposed

to setting up the operation directly using the appropriate flash controller peripheral registers). Whether the write operation is triggered by an AHB memory write or by

writing a control sequence to the flash controller registers, the same security and operational restrictions apply in either case. The operation proceeds in the same

manner in both cases regardless of the method that was used to trigger it.

The beginning of program flash memory (starting at address 0x0000_0000) is also the default location for the ARM exception/interrupt vector table. Since this table

contains initialization information such as the reset vector address which is required for the system to properly initialize, this table must be loaded into the flash in

order for the

MAX32600

to execute any application code.

The

MAX32600

supports multiple size options for the flash memory within the maximum possible space of 256 KB. The actual size of the memory is controlled by a

trim option loaded from the flash information block. When a size smaller than the maximum one is being used, the flash controller will respond to attempts to access

out-of-range addresses within the 256 KB range by setting an interrupt flag and returning a fixed "invalid access" data result pattern.

2.5.2

2 KB Instruction Cache

The 2 KB (512 x 32 or 256 x 64) instruction cache is used to cache the content of recently accessed locations in the program flash array to improve execution

throughput. Instruction fetches go to the instruction cache, which either returns the previously cached data (cache hit) or fetches the requested data from the flash

(cache miss) and stores it for future access.

Rev.1.3 April 2015

Maxim Integrated

Page 13

Содержание MAX32600

Страница 1: ...MAX32600 User s Guide April 2015...