Intel

®

81341 and 81342 I/O Processors

December 2007

Developer’s Manual

Order Number: 315037-002US

807

Timers—Intel

®

81341 and 81342

12.0 Timers

This chapter describes the Intel XScale

®

processor dual-programmable 32-bit timers

and Watch Dog Timer. Topics include timer registers (TMRx, TCRx and TRRx), timer

operation, timer interrupts, and timer register values at initialization.

Each timer is programmed by the timer registers. These registers are mapped into Intel

XScale

®

processor Coprocessor 6, registers 0 to 8. They may be accessed/manipulated

with the MCR, MRC, STC, and LDC instructions. The CRn field of the instruction denotes

the register number to be accessed. The opcode_1 and opcode_2 fields of the

instruction should be zero. The CRm field of the instruction should be nine. Most

systems restrict access to CP6 to privileged processes. To control access to CP6, use

the Coprocessor Access Register.

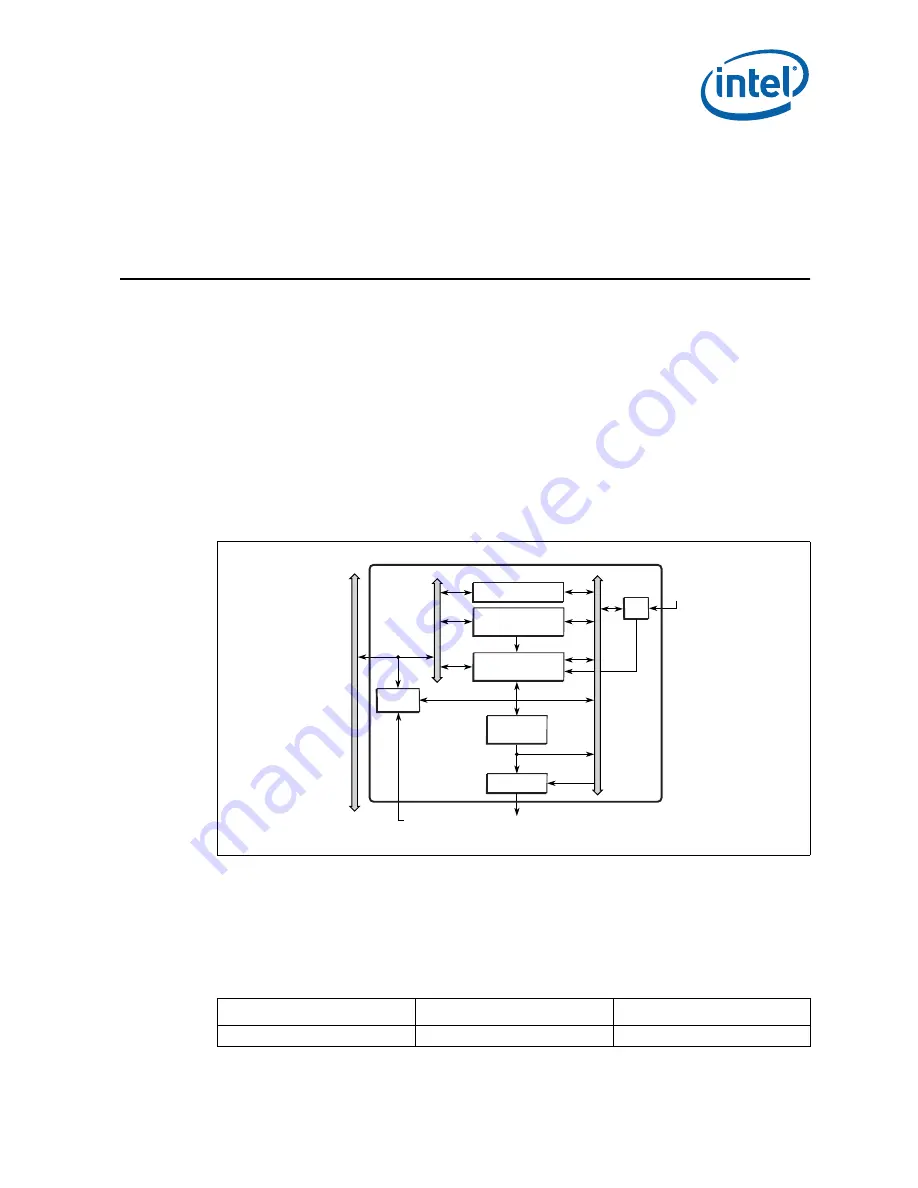

shows a diagram of the timer functions. See also

for the

Programmable Timer state diagram.

When enabled, a timer decrements the user-defined count value with each Timer Clock

(TCLOCK) cycle. The countdown rate is also user-configurable to be equal to the

internal bus frequency, or the internal bus clock rate divided by 4, 8 or 16. The timers

can be programmed to either stop when the count value reaches zero (single-shot

mode) or run continuously (auto-reload mode). When a timer’s count reaches zero, the

timer’s interrupt unit signals the processor’s interrupt controller.

Figure 116. Programmable Timer Functional Diagram

A6769-01

Timer Mode Register

Timer Reload Register

32-Bit Register

Timer Count Register

32-Bit Register

32-Bit Compare

Against Zero

Interrupt Unit

Clock

Unit

Selected

Clock

Bus

Clock

Terminal Count

Address

Detect

Internal

CPU

Bus

Interrupt

Output

User/

Privileged Mode

Table 491. Timer Performance Ranges

Internal Bus Frequency (MHz)

Max Resolution (ns)

Max Range (mins)

400

2.5

2.86