36

PSoC CY8CTMG20x and CY8CTST200 TRM, Document No. 001-53603 Rev. *C

Supervisory ROM (SROM)

An

MVI A, [expr]

instruction is used to move data from

SRAM into Flash. Therefore, use the

MVI

read pointer

(MVR_PP register) to specify which SRAM page from which

data is pulled. Using the

MVI

read pointer and the parameter

blocks POINTER value allows the SROM WriteBlock func-

tion to move data from any SRAM page into any Flash block.

The SRAM address, the first of the 128 bytes to store in

Flash, is indicated using the POINTER variable in the

parameter block (SRAM address FBh).

3.1.2.4

EraseBlock Function

The EraseBlock function is not recommended for use. The

functionality is redundant with the WriteBlock and WriteAnd-

Verify functions. The only practical use is for clearing all data

in a 128 byte block of contiguous bytes in Flash to 0x00. If

used, it should not be called repeatedly on the same block. It

may be used between WriteAndVerify or WriteBlock opera-

tions.

If write protection is turned on, then the EraseBlock function

exits, setting the accumulator and KEY2 back to 00h. KEY1

has a value of 01h, indicating a write failure.

To set up the parameter block for the EraseBlock function,

store the correct key values in KEY1 and KEY2. The block

number to erase must be stored in the BLOCKID variable.

3.1.2.5

ProtectBlock Function

The PSoC devices offer Flash protection on a block-by-

block basis.

Table 3-10

lists the protection modes available.

In the table, ER and EW indicate the ability to perform exter-

nal reads and writes (that is, by an external programmer).

For internal writes, IW is used. Internal reading is always

permitted by way of the

ROMX

instruction. An SR indicates

the ability to read by way of the SROM ReadBlock function.

In this table, note that all protection is removed by EraseAll.

3.1.2.6

TableRead Function

The TableRead function gives the user access to part-spe-

cific data stored in the Flash during manufacturing. The

Flash for these tables is separate from the program Flash

and is not directly accessible. It also returns a revision ID for

the die (do not confuse this with the silicon ID stored in the

Table 0 row in

Table 3-14

).

There are four 8-byte tables in the CY8CTMG20x,

CY8CTST200 devices.

3.1.2.7

EraseAll Function

The EraseAll function performs a series of steps that

destroys the user data in the Flash banks and resets the

protection block in each Flash bank to all zeros (the unpro-

tected state). This function is only executed by an external

programmer. If EraseAll is executed from code, the M8C

HALTs without touching the Flash or protections. See

Table

3-13

. The three other hidden blocks above the protection

block, in each Flash bank, are not affected by the EraseAll.

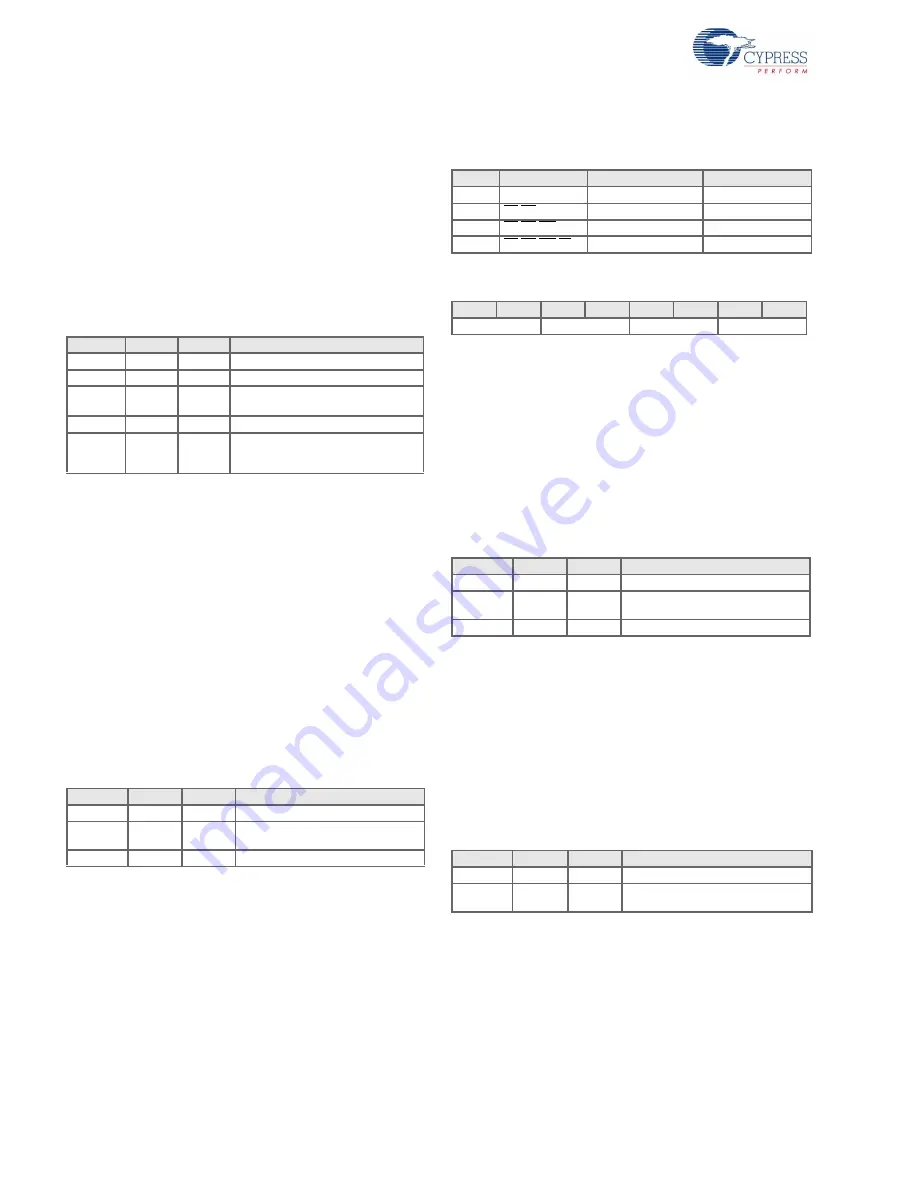

Table 3-8. WriteBlock Parameters (02h)

Name

Address

Type

Description

MVR_PP

0,D4h

Register

MVI

read page pointer register.

KEY1

0,F8h

RAM

3Ah.

KEY2

0,F9h

RAM

Stack Pointer value+3, when

SSC

is

executed.

BLOCKID

0,FAh

RAM

Flash block number.

POINTER

0,FBh

RAM

First of 128 addresses in SRAM, where

the data to be stored in Flash, is located

before calling WriteBlock.

Table 3-9. EraseBlock Parameters (03h)

Name

Address

Type

Description

KEY1

0,F8h

RAM

3Ah.

KEY2

0,F9h

RAM

Stack Pointer value+3, when SSC is

executed.

BLOCKID

0,FAh

RAM

Flash block number.

Table 3-10. Protect Block Modes

Mode

Settings

Description

In PSoC Designer

00b

SR ER EW IW

Unprotected

U = Unprotected

01b

SR ER EW IW

Read protect

F = Factory upgrade

10b

SR ER EW IW

Disable external write

R = Field upgrade

11b

SR ER EW IW

Disable internal write

W = Full protection

Table 3-11. Protection Level Bit Packing

7

6

5

4

3

2

1

0

Block n+3

Block n+2

Block n+1

Block n

Table 3-12. TableRead Parameters (06h)

Name

Address

Type

Description

KEY1

0,F8h

RAM

3Ah.

KEY2

0,F9h

RAM

Stack Pointer value+3, when

SSC

is

executed.

BLOCKID

0,FAh

RAM

Table number to read.

Table 3-13. EraseAll Parameters (05h)

Name

Address

Type

Description

KEY1

0,F8h

RAM

3Ah.

KEY2

0,F9h

RAM

Stack Pointer value+3, when

SSC

is

executed.

Summary of Contents for PSoC CY8CTMG20 Series

Page 4: ...4 Contents Overview Feedback...

Page 26: ...26 PSoC CY8CTMG20x and CY8CTST200 TRM Document No 001 53603 Rev C Section B PSoC Core Feedback...

Page 82: ...82 PSoC CY8CTMG20x and CY8CTST200 TRM Document No 001 53603 Rev C Sleep and Watchdog Feedback...

Page 134: ...134 PSoC CY8CTMG20x and CY8CTST200 TRM Document No 001 53603 Rev C I2C Slave Feedback...

Page 142: ...142 PSoC CY8CTMG20x and CY8CTST200 TRM Document No 001 53603 Rev C System Resets Feedback...

Page 160: ...160 PSoC CY8CTMG20x and CY8CTST200 TRM Document No 001 53603 Rev C SPI Feedback...

Page 182: ...182 PSoC CY8CTMG20x and CY8CTST200 TRM Document No 001 53603 Rev C Full Speed USB Feedback...

Page 302: ...302 PSoC CY8CTMG20x and CY8CTST200 TRM Document No 001 53603 Rev C Glossary Feedback...