PSoC CY8CTMG20x and CY8CTST200 TRM, Document No. 001-53603 Rev. *C

RAM Paging

ISR, the ISR is also required to restore the value before exe-

cuting the

RETI

instruction.

When the upper bit of the PgMode bits is set to ‘1‘, all nor-

mal memory access is forced to the SRAM page indicated

by the CUR_PP register value.

Table 4-1

summarizes the

PgMode bit values and the corresponding Memory Paging

mode.

4.1.6

Index Memory Page Pointer

The Source Indexed and Destination Indexed addressing

modes to SRAM are treated as a unique addressing mode

in a PSoC device with more than one page of SRAM. An

example of an indexed addressing mode is the

MOV A,

[X+expr]

instruction. Register access has indexed

addressing as well; however, those instructions are not

affected by the SRAM paging architecture.

Important Note

INT_CLR2

If you are not using assembly to

program a PSoC device, be aware that the

writer

may restrict the use of some memory paging modes.

Review the conventions in your compiler’s user guide for

more information on restrictions or conventions associated

with memory paging modes.

Indexed SRAM accesses operate in one of three modes:

■

Index memory access modes are forced to SRAM

Page 0.

■

Index memory access modes are directed to the SRAM

page indicated by the value in the STK_PP register.

■

Index memory access is forced to the SRAM page indi-

cated by the value in the IDX_PP register.

The mode is determined by the value of the PgMode bits in

the CPU_F register. However, the final SRAM page that is

used also requires setting either the Stack Page Pointer

(STK_PP) register or the Index Page Pointer (IDX_PP) reg-

ister. The table below shows the three indexed memory

access modes. The third column of the table is provided for

reference only.

After reset, the PgMode bits are set to 00b. In this mode,

index memory accesses are forced to SRAM Page 0, just as

they are in a PSoC device with only 256 bytes of SRAM.

This mode is also automatically enabled when an interrupt

occurs in a PSoC device and is considered the default ISR

mode. This is because before the ISR is entered, the M8C

pushes the current value of the CPU_F register onto the

stack and then clears the CPU_F register. Thus, by default,

any indexed memory access in an ISR is guaranteed to

occur in SRAM Page 0. When the

RETI

instruction executes

to end the ISR, the previous value of the CPU_F register is

restored as is the previous page mode. Note that this ISR

behavior is the default and that the PgMode bits in the

CPU_F register may be changed while in an ISR. If the

PgMode bits are changed while in an ISR, the pre-ISR value

is still restored by the

RETI

; but if the STK_PP or IDX_PP

registers are changed in the ISR, the ISR is also required to

restore the values before executing the

RETI

instruction.

The most likely PgMode bit change, while in an ISR, is from

the default value of 00b to 01b. In the 01b mode, indexed

memory access is directed to the SRAM page indicated by

the value of the STK_PP register. By using the PgMode,

modification of the STK_PP register value is unnecessary.

The STK_PP register determines on which SRAM page the

stack is located. The 01b paging mode is intended to pro-

vide easy access to the stack, while in an ISR, by setting the

CPU_X register (just X in instruction format) equal to value

of SP using

MOV X, SP

instruction.

The two previous paragraphs covered two of the three

indexed memory access modes: STK_PP and forced to

SRAM Page 0. Note, as shown in

Table 4-1

, that the

STK_PP mode for indexed memory access is available

under two PgMode settings. The 01b mode is intended for

ISR use and the 11b mode is intended for non-ISR use. The

third indexed memory access mode requires the PgMode

bits to be set to 10b. In this mode indexed memory access is

forced to the SRAM page indicated by the value of the

IDX_PP register.

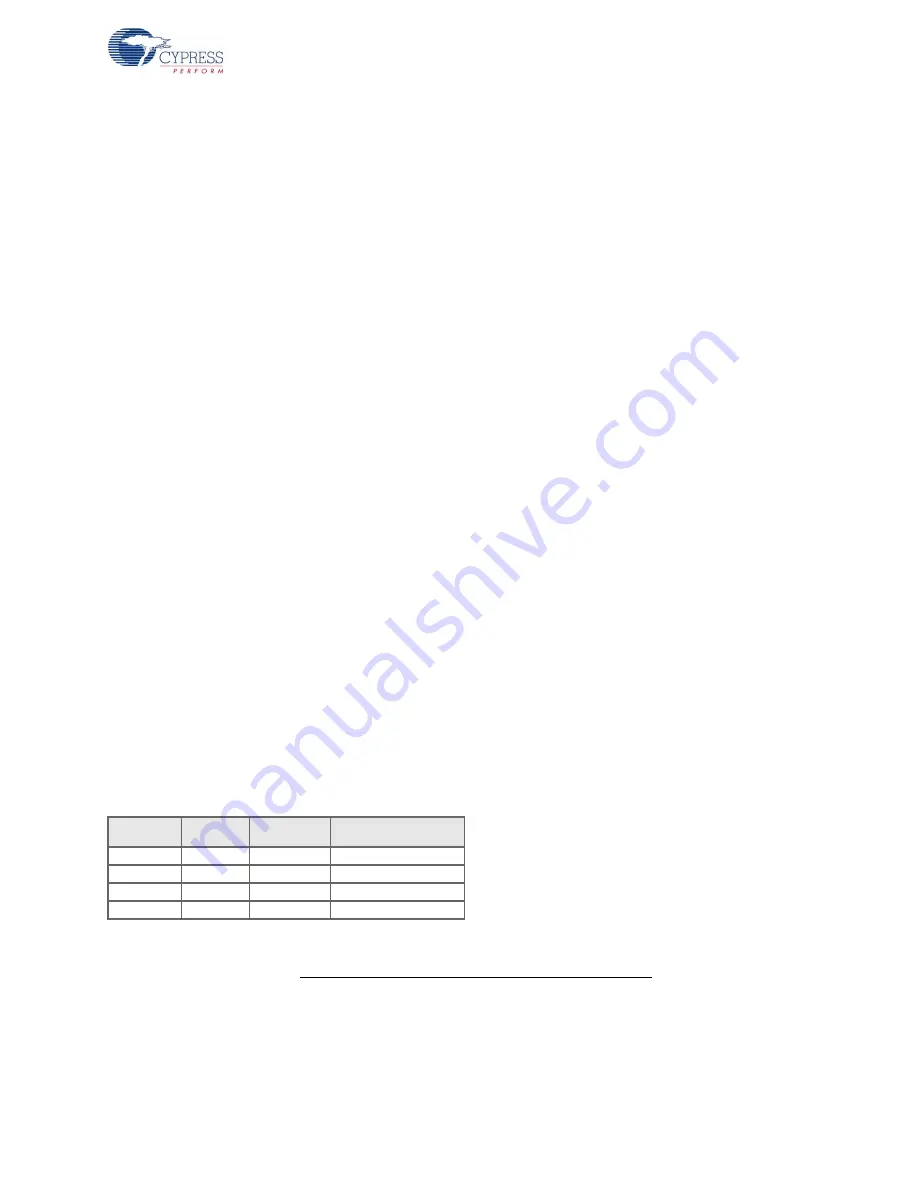

Table 4-1. CPU_F PgMode Bit Modes

CPU_F

PgMode BIts

Current

SRAM Page

Indexed

SRAM Page

Typical Use

00b

0

0

ISR*

01b

0

STK_PP

ISR with variables on stack

10b

CUR_PP

IDX_PP

11b

CUR_PP

STK_PP

*

Mode used by SROM functions initiated by the

SSC

instruction.

Summary of Contents for PSoC CY8CTMG20 Series

Page 4: ...4 Contents Overview Feedback...

Page 26: ...26 PSoC CY8CTMG20x and CY8CTST200 TRM Document No 001 53603 Rev C Section B PSoC Core Feedback...

Page 82: ...82 PSoC CY8CTMG20x and CY8CTST200 TRM Document No 001 53603 Rev C Sleep and Watchdog Feedback...

Page 134: ...134 PSoC CY8CTMG20x and CY8CTST200 TRM Document No 001 53603 Rev C I2C Slave Feedback...

Page 142: ...142 PSoC CY8CTMG20x and CY8CTST200 TRM Document No 001 53603 Rev C System Resets Feedback...

Page 160: ...160 PSoC CY8CTMG20x and CY8CTST200 TRM Document No 001 53603 Rev C SPI Feedback...

Page 182: ...182 PSoC CY8CTMG20x and CY8CTST200 TRM Document No 001 53603 Rev C Full Speed USB Feedback...

Page 302: ...302 PSoC CY8CTMG20x and CY8CTST200 TRM Document No 001 53603 Rev C Glossary Feedback...