User Manual

487

Rev. 1.1

2019-03-18

TLE984xQX

Microcontroller with LIN and Power Switches for Automotive Applications

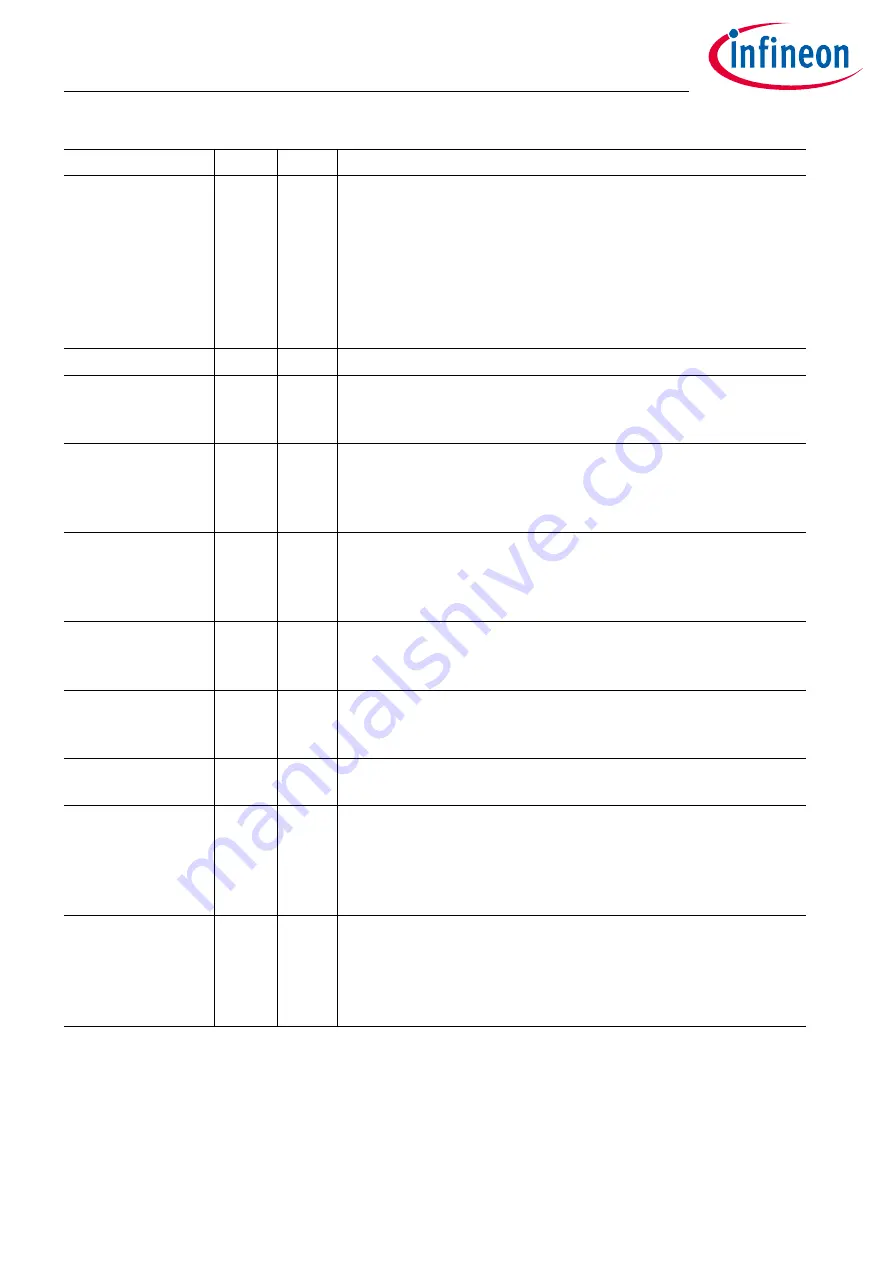

General Purpose Timer Units (GPT12)

CI

13:12

rw

Register CAPREL Capture Trigger Selection

1)

00

B

Disabled

, Capture disabled

01

B

Positive

, Positive transition (rising edge) on CAPIN

2)

or any

transition on T3IN

10

B

Negative

, Negative transition (falling edge) on CAPIN or any

transition on T3EUD

11

B

Any

, Any transition (rising or falling edge) on CAPIN or any

transition on T3IN or T3EUD

RES

11

r

Reserved

CT3

10

rw

Timer T3 Capture Trigger Enable

0

B

CAPIN

, Capture trigger from input line CAPIN

1

B

T3IN

, Capture trigger from T3 input lines T3IN and/or T3EUD

T5RC

9

rw

Timer T5 Remote Control

0

B

T5R

, Timer T5 is controlled by its own run bit T5R

1

B

T6R

, Timer T5 is controlled by the run bit T6R of core timer T6,

not by bit T5R

T5UDE

8

rw

Timer T5 External Up/Down Enable

3)

0

B

T5UD

, Count direction is controlled by bit T5UD;

input T5EUD is disconnected

1

B

T5EUD

, Count direction is controlled by input T5EUD

T5UD

7

rw

Timer T2 Up/Down Control

0

B

Up

, Timer T5 counts up

1

B

Down

, Timer T5 counts down

T5R

6

rw

Timer T5 Run Bit

0

B

Stop

, Timer T5 stops

1

B

Run

, Timer T5 runs

RES

5

r

Reserved

Contains the current value of the CAPREL register

T5M

4:3

rw

Timer T5 Input Mode Control

00

B

Timer Mode

,

01

B

Counter Mode

,

10

B

Gated low

, Gated Timer Mode with gate active low

11

B

Gated high

, Gated Timer Mode with gate active high

T5I

2:0

rw

Timer T5 Input Parameter Selection

Depends on the operating mode, see respective sections for

encoding:

for Timer Mode and Gated Timer Mode

Counter Mode

1) To define the respective trigger source signal, also bit CT3 must be regarded (see

2) Rising edge must be selected if capturing is triggered by the internal GPT1 read signals (see register PISEL and

“Combined Capture Modes” on Page 480

).

3) See

for encoding of bits T5UD and T5UDE.

Field

Bits

Type

Description