Chapter 10 PCI Controller

10-40

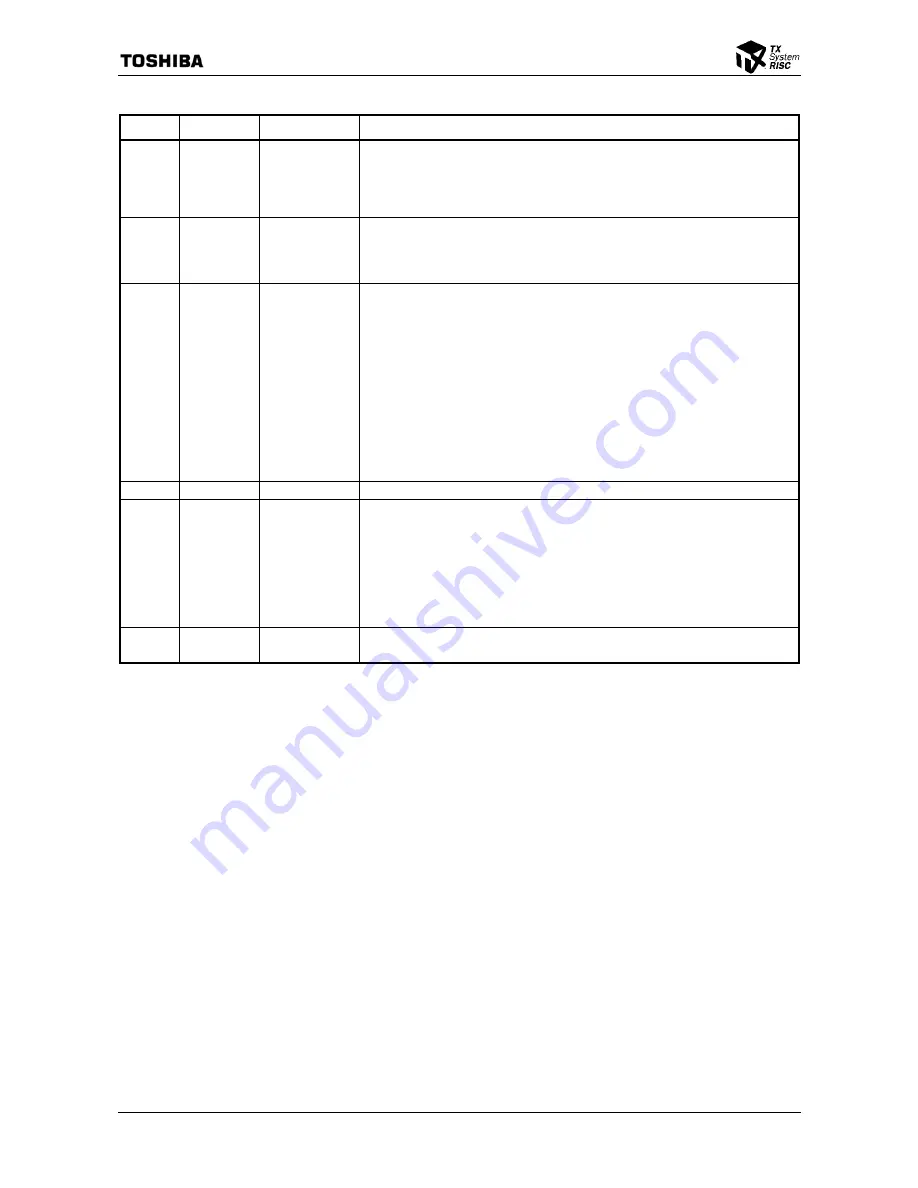

Bits Mnemonic Field

Name

Description

5 G2PM2EN

Initiator Memory

Space 2 Enable

Initiator Memory Space 2 Enable (Initial value: Normal Mode: 0; PCI Boot Mode: 1,

R/W)

Controls PCI initiator access to Memory Space 2.

1: Memory Space 2 is valid.

0: Memory Space 2 is invalid.

4 G2PIOEN

Initiator I/O Space

Enable

Initiator I/O Space Enable (Initial value: 0, R/W)

Controls PCI initiator access to the I/O Space..

1: I/O Space is valid.

0: I/O Space is invalid.

3 IRBER

Bus Error

Response Setting

During Initiator

Access

Initiator Access Bus Error Response (Initial value: 1, R/W)

Bus error responses on the G-Bus are controlled when the following phenomena

indicated by the PCI Status, Command Register (PICSTATUS) and the G2P Status

Register (G2PSTATUS) occur during initiator Read access.

Detected Fatal Error (G2PSTATUS.MDFE)

Detected Parity Error (G2PSTATUS.MDPE)

Received Master Abort (PCISTATUS.RMA)

Received Target Abort (PCISTATUS.RTA)

Initiator Detected TRDY Time Out Error (G2PSTATUS.IDTTOE)

Initiator Detected Retry Time Out Error (G2PSTATUS.IDRTOE)

1: Responds with a Bus error on the G-Bus.

0: Does not respond with a Bus error on the G-Bus. (Normally terminates the

transaction on the G-Bus. Read data is invalid.)

2

⎯

Reserved

⎯

1 BSWAPI

Byte Swap for

Indirect, Config,

IACK, and

Special cycle

Byte Swap for Indirect, Config, IACK, and Special cycle

(Initial value: Little Endian Mode: 0; Big Endian Mode: 1, R/W)

Sets the byte swapping of Indirect, Config, IACK, and Special cycle.

0: Do not perform byte swapping.

1: Perform byte swapping.

Please use the default state in most situations. If this bit is changed to “0” when in the

Big Endian Mode, the byte order of transfer to Memory Space 0 through DWORD (32-

bit) access will not change.

0

ASERR

Assert SERR

Assert SERR (Initial value: 0, R/W1C)

A write of 1 will assert SERR for 1 PCI clock. Always read 0.

Figure 10.4.13 G2P Configuration Register (2/2)

Summary of Contents for TMPR4925

Page 1: ...64 Bit TX System RISC TX49 Family TMPR4925 Rev 3 0 ...

Page 4: ......

Page 15: ...Handling Precautions ...

Page 16: ......

Page 18: ...1 Using Toshiba Semiconductors Safely 1 2 ...

Page 40: ...3 General Safety Precautions and Usage Considerations 3 18 ...

Page 42: ...4 Precautions and Usage Considerations 4 2 ...

Page 43: ...TMPR4925 ...

Page 44: ......

Page 54: ...Chapter 1 Features 1 8 ...

Page 58: ...Chapter 2 Block Diagram 2 4 ...

Page 88: ...Chapter 4 Address Mapping 4 12 ...

Page 226: ...Chapter 8 DMA Controller 8 58 ...

Page 260: ...Chapter 9 SDRAM Controller 9 34 ...

Page 480: ...Chapter 15 Interrupt Controller 15 32 ...

Page 554: ...Chapter 19 Real Time Clock RTC 19 8 ...

Page 555: ...Chapter 20 Removed 20 1 20 Removed ...

Page 556: ...Chapter 20 Removed 20 2 ...

Page 564: ...Chapter 21 Extended EJTAG Interface 21 8 ...

Page 580: ...Chapter 22 Electrical Characteristics 22 16 ...

Page 588: ...Chapter 24 Usage Notes 24 2 ...