Chapter 7 External Bus Controller

7-59

7.6

Flash ROM, SRAM Usage Example

Figure 7.6.1 illustrates example Flash ROM connections, and Figure 7.6.2 illustrates example SRAM

connections. Also, Figure 7.6.3 illustrates example connections with the SDRAM and the bus separated.

Since connecting multiple memory devices such as SDRAM and ROM onto a single bus increases the

load, 100 MHz class high-speed SDRAM access may not be performed normally. As a corrective measure,

there is a way of reducing the bus load by connecting a device other than SDRAM via a buffer. If such a

method is employed, directional control becomes necessary since the data becomes bidirectional.

The TX4925 prepares the BUSSPRT* signal for performing data directional control (see Figure 7.6.3).

BUSSPRT* is asserted when the External Bus Controller channel is active and a Read operation is being

performed.

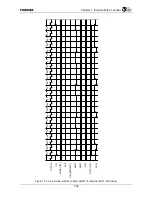

Figure 7.6.1 Flash ROM (x16 Bits) Connection Example (32-bit Data Bus)

Figure 7.6.2 SRAM (x16 Bits) Connection Example (32-bit Data Bus)

ADDR[19:0]

UAE

CE

*

[0]

SWE

*

OE

*

DATA[31:0]

TX4925

ADDR[19:0]

A[19:0]

A20

CE

*

WE

*

OE

*

D[15:0]

ADDR[12]

(ADDR[20])

A[19:0]

A20

CE

*

WE

*

OE

*

D[15:0]

Flash ROM (x16 bits)

D[31:16]

D[15:0]

D[31:16]

BWE

*

[3:0]

ADDR[19:0]

CE

*

[1]

SWE

*

OE

*

DATA[31:0]

TX4925

ADDR[19:0]

UB LB

A[19:0]

CS

*

WE

*

OE

*

D[15:0]

SRAM (x16 Bits)

D[15:0]

UB LB

A[19:0]

CS

*

WE

*

OE

*

D[15:0]

BWE

*

[3]

BWE

*

[2]

BWE

*

[1]

BWE

*

[0]

Summary of Contents for TMPR4925

Page 1: ...64 Bit TX System RISC TX49 Family TMPR4925 Rev 3 0 ...

Page 4: ......

Page 15: ...Handling Precautions ...

Page 16: ......

Page 18: ...1 Using Toshiba Semiconductors Safely 1 2 ...

Page 40: ...3 General Safety Precautions and Usage Considerations 3 18 ...

Page 42: ...4 Precautions and Usage Considerations 4 2 ...

Page 43: ...TMPR4925 ...

Page 44: ......

Page 54: ...Chapter 1 Features 1 8 ...

Page 58: ...Chapter 2 Block Diagram 2 4 ...

Page 88: ...Chapter 4 Address Mapping 4 12 ...

Page 226: ...Chapter 8 DMA Controller 8 58 ...

Page 260: ...Chapter 9 SDRAM Controller 9 34 ...

Page 480: ...Chapter 15 Interrupt Controller 15 32 ...

Page 554: ...Chapter 19 Real Time Clock RTC 19 8 ...

Page 555: ...Chapter 20 Removed 20 1 20 Removed ...

Page 556: ...Chapter 20 Removed 20 2 ...

Page 564: ...Chapter 21 Extended EJTAG Interface 21 8 ...

Page 580: ...Chapter 22 Electrical Characteristics 22 16 ...

Page 588: ...Chapter 24 Usage Notes 24 2 ...