Chapter 8 DMA Controller

8-25

Bits Mnemonic Field

Name

Description

26 DBINH

Destination Burst

Inhibit

Destination Burst Inhibit (Initial value: 0, R/W)

During Dual Address transfer, this bit sets whether to perform Burst transfer or Single

transfer on a Write cycle to the address set from FIFO to DMDARn when Burst

transfer is set by DMCCRn.XFSZ. Refer to “8.3.8.2 Burst Transfer During Dual

Address Transfer” for more information.

1: Multiple Single transfers are executed.

0: Burst transfer is executed.

25 SBINH

Source Burst

Inhibit

Source Burst Inhibit (Initial value: 0, R/W)

During Dual Address transfer, this bit sets whether to perform Burst transfer or Single

transfer on a Read cycle to the FIFO from the address set to DMSARn when Burst

transfer is set by DMCCRn.XFSZ. Refer to “8.3.8.2 Burst Transfer During Dual

Address Transfer” for more information.

The settings of this bit have no effect during Single Address transfers.

1: Multiple Single transfers are executed.

0: Burst transfer is executed.

24

CHRST

Channel Reset

Channel Reset (Initial value: 1, R/W)

This bit is used for initializing channels. The DMCCRn.XFACT, DMCCRn.CHNEN,

and DMCSRn bits are all cleared. In addition, all channel logic and interrupts from

channels are cleared and bus ownership requests to the DMA Channel Arbiter are

also reset. The software must clear this bit before operating a channel.

1: Reset channel

0: Enable channel

23

REVBYTE

Reverse Byte

Reverse Bytes (Initial value: 0, R/W)

This bit specifies whether to reverse the byte order during a Dual Address transfer

when the Transfer Setting Size field (DMCCRn.XFSZ) setting is 4 bytes or more.

Refer to “0

Double Word Byte Swapping” for more information.

1: Reverses the byte order.

0: Does not reverse the byte order.

22 ACKPOL

Acknowledge

Polarity

Acknowledge Polarity (Initial value: 0, R/W)

Specifies the polarity of the DMAACK[n] signal.

1: Asserts when the DMAACK[n] signal is High

0: Asserts when the DMAACK[n] signal is Low

21

REQPL

Request Polarity

Request Polarity (Initial value: 0, R/W)

Specifies the polarity of the DMAREQ[n] signal.

1: Asserts when the DMAREQ[n] signal is High.

0: Asserts when the DMAREQ[n] signal is Low.

20

EGREQ

Edge Request

Edge Request (Initial value: 0, R/W)

Specifies the method for detecting DMA requests by the DMAREQ[n] signal.

1: DMAREQ[n] signal is Edge Detect.

0: DMAREQ[n] signal is Level Detect.

19 CHDN

Chain

Complete

Chain Done (Initial value: 0, R/W)

Selects control by the DMADONE

*

signal. See “8.3.3.4 DMA Controller” for more

information.

1: Assertion of the DMADONE

*

signal controls the overall Chain DMA transfer.

0: Assertion of the DMADONE

*

signal controls DMA transfer according to the DMA

Channel Register setting at that time.

18:17

DNCTL

DONE Control

Done Control (Initial value: 00, R/W)

Specifies the input/output mode of the DMADONE

*

signal. Refer to “8.3.3.4

DMADONE* Signal” for more information.

00: DMADONE

*

signal becomes the input signal, but input is ignored.

01: DMADONE

*

signal becomes the input signal.

10: DMADONE

*

signal becomes the output signal.

11: DMADONE

*

signal becomes the open drain input/output signal.

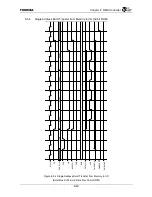

Figure 8.4.2 DMA Channel Control Register (2/4)

Summary of Contents for TMPR4925

Page 1: ...64 Bit TX System RISC TX49 Family TMPR4925 Rev 3 0 ...

Page 4: ......

Page 15: ...Handling Precautions ...

Page 16: ......

Page 18: ...1 Using Toshiba Semiconductors Safely 1 2 ...

Page 40: ...3 General Safety Precautions and Usage Considerations 3 18 ...

Page 42: ...4 Precautions and Usage Considerations 4 2 ...

Page 43: ...TMPR4925 ...

Page 44: ......

Page 54: ...Chapter 1 Features 1 8 ...

Page 58: ...Chapter 2 Block Diagram 2 4 ...

Page 88: ...Chapter 4 Address Mapping 4 12 ...

Page 226: ...Chapter 8 DMA Controller 8 58 ...

Page 260: ...Chapter 9 SDRAM Controller 9 34 ...

Page 480: ...Chapter 15 Interrupt Controller 15 32 ...

Page 554: ...Chapter 19 Real Time Clock RTC 19 8 ...

Page 555: ...Chapter 20 Removed 20 1 20 Removed ...

Page 556: ...Chapter 20 Removed 20 2 ...

Page 564: ...Chapter 21 Extended EJTAG Interface 21 8 ...

Page 580: ...Chapter 22 Electrical Characteristics 22 16 ...

Page 588: ...Chapter 24 Usage Notes 24 2 ...