Chapter 8 DMA Controller

8-50

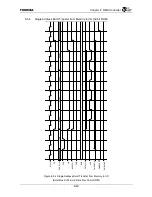

8.5.13 Single Address Single Transfer from Memory to I/O (32-bit SDRAM)

Figure 8.5.14 Single Address Single Transfer from Memory to I/O

(Single Read of 32-bit Data from 32-bit SDRAM)

00

00

S

DCL

K

CS

*

A

DDR [1

9

:5

]

RA

S

*

OE

*

/

BU

S

SPR

T

*

WE

*

DQ

M

[7

:0

]

D

A

T

A

[

3

1:

0]

AC

K

*

D

M

AR

EQ[

n

]

DM

A

A

CK

[n

]

DM

A

D

O

N

E

*

0

080

ff

CA

S

*

CK

E

*

f0

ff

0

081

0

00001

00

fffff

e

e

f

Summary of Contents for TMPR4925

Page 1: ...64 Bit TX System RISC TX49 Family TMPR4925 Rev 3 0 ...

Page 4: ......

Page 15: ...Handling Precautions ...

Page 16: ......

Page 18: ...1 Using Toshiba Semiconductors Safely 1 2 ...

Page 40: ...3 General Safety Precautions and Usage Considerations 3 18 ...

Page 42: ...4 Precautions and Usage Considerations 4 2 ...

Page 43: ...TMPR4925 ...

Page 44: ......

Page 54: ...Chapter 1 Features 1 8 ...

Page 58: ...Chapter 2 Block Diagram 2 4 ...

Page 88: ...Chapter 4 Address Mapping 4 12 ...

Page 226: ...Chapter 8 DMA Controller 8 58 ...

Page 260: ...Chapter 9 SDRAM Controller 9 34 ...

Page 480: ...Chapter 15 Interrupt Controller 15 32 ...

Page 554: ...Chapter 19 Real Time Clock RTC 19 8 ...

Page 555: ...Chapter 20 Removed 20 1 20 Removed ...

Page 556: ...Chapter 20 Removed 20 2 ...

Page 564: ...Chapter 21 Extended EJTAG Interface 21 8 ...

Page 580: ...Chapter 22 Electrical Characteristics 22 16 ...

Page 588: ...Chapter 24 Usage Notes 24 2 ...